В зависимости от типа применяемых элементов и особенностей схемотехники различают следующие семейства ЦИС: ТЛНС— транзисторные логические ИС с непосредственной (гальванической) связью; РТЛ — резисторно-транзисторные логические ИС; PЕТЛ резисторно-емкостные логические ИС; ДТЛ —диодно-транзисторные логические ИС; ТТЛ — транзисторно-транзисторные логические ИС; И2Л—интегральные инжекционные логические схемы; ЭСЛ—эмиттерно-связанные логические ИС; МДП —логические схемы на основе МДП транзисторов; КМДП — логические схемы на основе комплементарных МДП транзисторов. Чтобы правильно выбрать тип ЦИС, необходимо представлять внутреннюю структуру базовых логических элементов, знать функциональные возможности и основные параметры логических элементов разных семейств.

Исторически первым было семейство ЦИС типа ТЛНС. Базовые элементы имеют технические решения, приведенные в табл. 3.1. Следует учитывать, что нагрузками логических элементов являются входные цепи аналогичных элементов. Серьезный недостаток ТЛНС- неравномерное распределение тока между базами нагрузочных транзисторов. Такая неравномерность связана с различием входных характеристик транзисторов, обусловленным не технологическим разбросом (который в ИС мал), а неизбежным различием коллекторных токов насыщенных транзисторов. Токи насыщения существенно зависят от числа транзисторов базового элемента, находящихся в открытом состоянии. При подключении нескольких нагрузок к базовому элементу снижается логический перепад выходных уровней и, следовательно, допустимое значение статических помех (до значения Uпом»0,2 В).

В семействе РТЛ используются технические решения, аналогичные ТЛНС, но для выравнивания входных характеристик транзисторов в цепях баз включены резисторы с сопротивлениями несколько сот Ом. При этом возросли уровень логической 1, логический перепад уровней и допустимое напряжение статической помехи, но снизилось быстродействие. Сопротивления в цепи базы и входные емкости oбразуют цепочки, из-за которых возрастает длительность фронта выходного импульса.

Для того чтобы избежать указанного недостатка в семействе РЕТЛ, явившемся развитием РТЛ, резисторы в цепях базы шунтированы конденсаторами небольшой емкости. В момент переключения предыдущего элемента эти конденсаторы на некоторое время шунтируют резисторы и обеспечивают повышенные значения базовых токов, тем самым снижая длительность фронта.

В ИС резисторы и особенно конденсаторы занимают большую плошать. Поэтому элементы семейства РТЛ и РЕТЛ оказались неперспективными и в настоящее время используются редко. Семейство ТЛНС явилось прототипом весьма перспективного варианта логических элементов семейства И2Л, рассматриваемого ниже.

В базовых элементах семейства ДТЛ отказались от резисторов и конденсаторов в цепях без транзисторов и используют вместо них диоды.

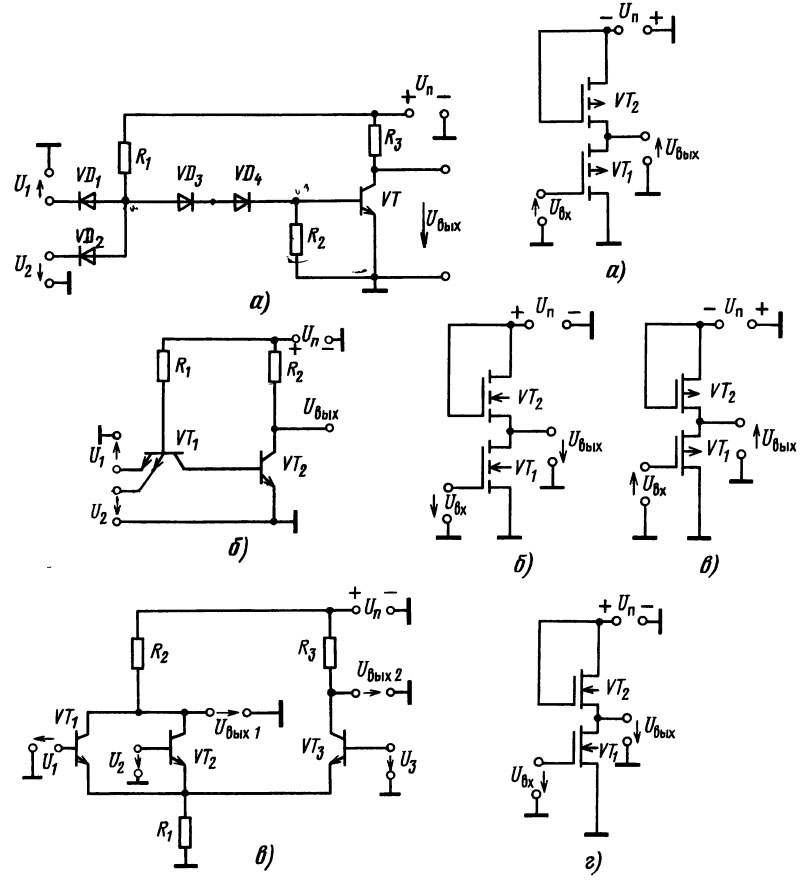

Базовый элемент семейства ДТЛ, выполняющий операцию И-НЕ, приведен на рис. 3.2,а.

В элементе ДТЛ базовый ток выходного транзистора, выполняющего функции инвертора, проходит через резистор R1, диоды VD1 и VD4 только тогда, когда закрыты оба входных диода VD1 и VD2, т. е. если все входные напряжения имеют высокий уровень (U1вх1, U1вх2). В этом случае транзистор VT открыт и на выходе имеется низкий уровень U0вых.

Базовый ток, протекающий через диоды VD3, VD4, вызывает на них падение напряжении около 1,2 В. Вместе с напряжением на базе открытого транзистора это составит U=1,2 + 0,6=1,8 В. Если входное напряжение не превышает 1,2 В, соответствующий входной диод открывается, а напряжение U3 снижается. Следовательно, диоды VD3, VD4, а вместе с ними и транзистор VT закрываются.

Рисунок 3.2

Введение в схему диодов VD3, VD4 способствует увеличению перепада логических уровней и помехоустойчивости элемента (Uпом»0,5 В). Для того чтобы работа диодов VD3, VD4 не зависала oт состояния транзистора VT, в схеме предусмотрено сопротивление R2.

В семействе ТТЛ удалось избежать основного недостатка элементов ДТЛ—большого количества диодов. В базовом элементе семейства ТТЛ (рис. 3.2, б) функции диодов выполняет входной многоэмиттерный транзистор VТ1.

Если все входные напряжения имеют высокий уровень, ток, протекающий через резистор R1 по открытому в прямом направлении переходу «база—коллектор» входного транзистора VT1, течет в базу транзистора VT2 и приводит его в открытое состояние. В этом случае на выходе транзистора VT2 будет низкий уровень U0вых. Если хотя бы на один из входов подано низкое напряжение, то соответствующий переход «база — эмиттер» открывается и отбирает базовый ток транзистора VT2. Транзистор VТ2 закрывается, и выходное напряжение принимает значение, соответствующее высокому уровню (U1вых). Таким образом, элемент выполняет операцию И-НЕ.

Базовый элемент семейства ТТЛ занимает существенно меньшую площадь по сравнению с элементом семейства ДТЛ, сохраняя его достоинства. Поэтому схемы ТТЛ в настоящее время практически вытеснили схемы ДТЛ и получили очень широкое pacпpостранение.

Для увеличения нагрузочной способности и повышения помехоустойчивости в ТТЛ схемах вместо простого инвертора на одном транзисторе часто используют специальные каскады усиления мощности на двух-трех транзисторах.

Для повышения быстродействия между базой и коллектором VТ2 включают диод Шотки. Как известно, максимальная частота переключения транзистора ограничивается в основном временем рассасывания накопленных зарядов. Для повышения максимальной частоты переключения необходимо предотвратить насыщение транзистора и этим исключить накопление заряда. Включение диода Шотки параллельно переходу «база —коллектор» транзистора приводит к возникновению ООС по напряжению и препятствует снижению напряжения между коллектором и эмиттером ниже 0,3 В.

Элементы транзисторной логики с диодами Шотки получили название ТТЛШ. Они имеют примерно в 3 раза меньшее среднее время задержки сигналов.

Базовый элемент семейства ЭСЛ имеет упрощенную схему, приведенную на рис. 3.2,в. Как видно из схемы, транзисторы VT1, VT2 и VT3 образуют дифференциальный усилитель, который может использоваться в качестве переключателя токов основных транзисторов VT1 либо VT2 и вспомогательного транзистора VТ3. Причем для переключения токов достаточна небольшая разность входных напряжений (примерно ±100 мВ). Нагрузочные сопротивления R2 и R3 выбирают низкоомными, чтобы предотвратить насыщение открытого транзистора.

Рассмотрим принцип работы базового элемента семейства ЭСЛ. На базу вспомогательного транзистора VТ3 подается постоянное опорное напряжение U°вх < Uоп < U1вх. Если все входные напряжения имеют низкий уровень (U1=U0вх, U2 = U0вх), транзисторы VТ1 и VT2 закрыты. В этом случае эмиттерный ток транзистора VТ3, протекая через резистор R1, вызывает на нем падение напряжения, являющееся для транзисторов VТ1 и VТ2 запирающим. Поэтому на первом выходе будет высокий уровень напряжения Uвых1 = U1вых, а на втором выходе—низкий Uвых2 = U0вых.

Если хотя бы на одном из входов напряжение будет иметь высокий уровень, то на сопротивлении R1 возрастет напряжение и транзистор VТ3 окажется в закрытом состоянии. При этом напряжение на первом выходе уменьшится (Uвых1 = U0вых), а на втором выходе увеличится (Uвых2 = U1вых). Таким образом, элемент может выполнять операции ИЛИ (при снятии выходного сигнала со второго выхода) либо ИЛИ-НЕ (при снятии выходного сигнала с первого выхода).

Базовые элементы семейства ЭСЛ потребляют значительную мощность от источника питания, однако обеспечивают наименьшее время переключения по сравнению с другими типами логических элементов. Среднее время задержки для элементов семейства ЭСЛ лежит в пределах десятых долей или единиц наносекунды. Несмотря на малый перепад логических уровней, элементы семейства ЭСЛ обладают удовлетворительной помехоустойчивостью. Импульсные помехи в цепях питания незначительны, так как потребление тока в схеме не изменяется при переключении ее элементов.

В реальных схемах на выходах логических элементов семейства ЭСЛ используют усилители мощности на основе эмиттерных повторителей, что улучшает их нагрузочную способность,

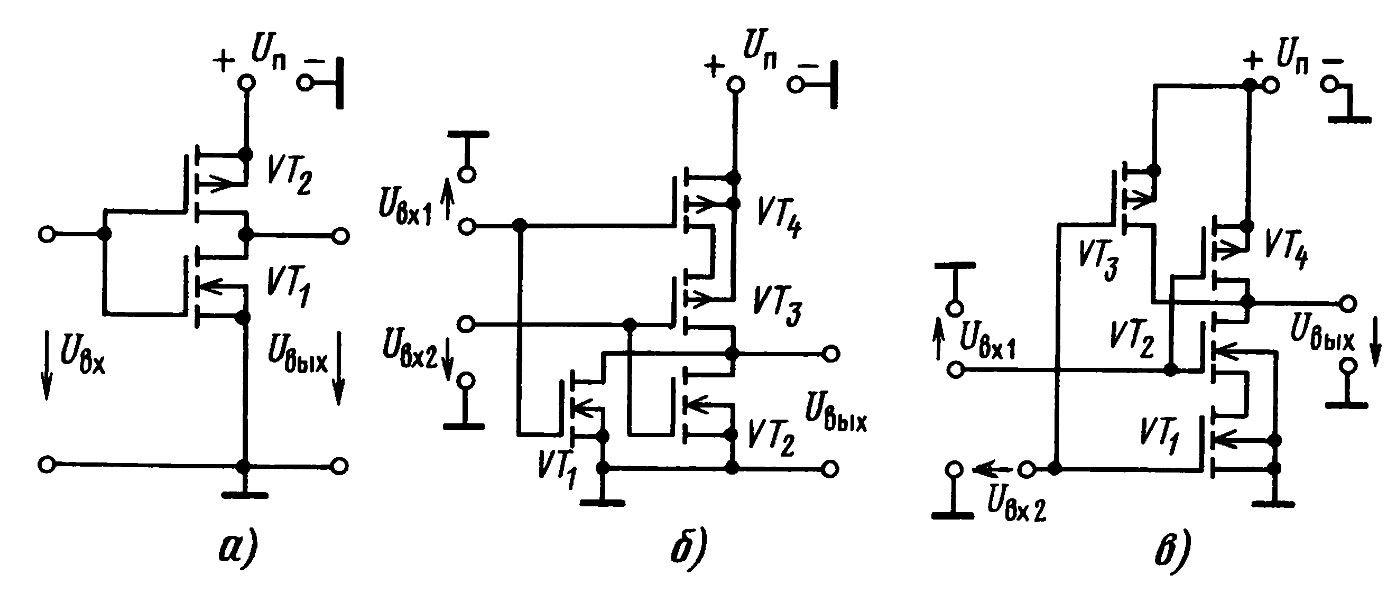

Семейство МДП содержит несколько типов базовых элементов на основе транзисторов: с индуцированным каналом р-типа, с индуцированным каналом n-типа, со встроенным каналом р-типа, со встроенным каналом n-типа. Схемы простейших базовые элементов названных типов, реализующих операцию НЕ, приведены на рис. 3.3. Здесь транзисторы VT1 выполняют функцию ключа, а транзисторы VT2 —функции нелинейных резисторов нагрузки. Использование транзисторов VТ2 в качестве нагрузочных элементов позволяет отказаться от создания высокоомных резисторов, что при интегральном исполнении дает возможность повышать плотность компоновки и создавать все элементы в едином технологическом цикле. Для поддержания транзисторов VТ2 в открытом состоянии их затворы соединяют с источником питания, как показано на рис. 3.3. Транзисторы VТ1 в схемах на рис. 3.2, а, б имеют индуцированные каналы и, следовательно, при отсутствии входного сигнала (Uвх=U0вх) закрыты. При этом на выходе напряжение соответствует логической 1 (Uвых = U1вых). Следует помнить, что р-канальные элементы работают в режиме отрицательной логики, n-канальные — в режиме положительной логики.

При подаче на входы отпирающего напряжения (Uвх=U1вх) транзисторы VТ1 открываются и на выходе напряжение принимает значение, соответствующее логическому 0 (Uвых = U0вых).

Таким образом, элементы выполняют функции инверторов и реализуют операцию НЕ. Аналогичным образом работают инверторы на основе транзисторов со встроенными каналами (рис. 3.3, в, г). Однако управлять такими транзисторами сложнее. Это объясняется тем, что в нормальном состоянии (при Uвх= 0) через транзисторы протекает некоторый ток. При этом Uвых = Uп за счет падения напряжения на транзисторах VТ1. Для надежного закрытия транзисторов VT1 требуется исходное напряжение смещения с полярностью, отличной от напряжения Uп

Рисунок 3.4

Логические элементы на основе МДП транзисторов имеют ряд особенностей:

1. Входные цепи практически не потребляют тока и, следовательно, не нагружают предшествующие элементы аналогичного типа. Таким образом, МДП логические элементы могут иметь очень большие значения коэффициентов разветвления по выходу. Его верхнее значение в основном определяется требуемым временем переключения, так как с ростом числа нагрузок пропорционально возрастет емкость нагрузки.

Несмотря на использование гальванической связи МДП, логические элементы функционируют независимо друг от друга. В частности, логические уровни U0вых и U1вых не зависят от числа подключенных входов следующих элементов.

Напряжение питания выбирают в 3 ... 4 раза больше порогового напряжения МДП транзисторов. Поэтому перспективными являются разработки с использованием низкопороговых МДП транзисторов (Uзи пор»1 В). Это позволяет синтезировать логические элементы семейства МДП, совместимые по уровням с другими семействами, в частности с ТТЛ. При этом МДП логические элементы обладают повышенной помехоустойчивостью (Uпом = 1 ... 2В).Элементы семейства МДП обладают невысоким быстро действием. Быстродействие ограничивается скоростью перезаряда емкости нагрузки. Для повышения быстродействия необходимо увеличивать рабочие токи. Это возможно путем увеличения ширины каналов и, следовательно, площади, занимаемой транзисторами. Увеличение рабочих токов связано с увеличением потребляемой мощности. Таким образом, повышение быстро действия логических МДП схем связано с неизбежным уменьшением степени интеграции.

Исторически первыми стали широко использоваться логические элементы на основе р-канальных транзисторов с индуцированными каналами, имеющие простую технологию изготовления (рис. 3.3, а). Затем были разработаны n-канальные логические элементы, обладающие повышенным быстродействием.

В настоящее время очень широко применяются логические элементы, использующие МДП транзисторы с разными типами проводимости каналов. Они выделились в самостоятельное семейство, получившее название комплементарной МДП логики (КМДП). Базовые технические решения семейства КМДП приведены на рис. 3.4.

Недостатком инверторов семейства МДП (рис. 3,3) является нахождение нагрузочных транзисторов (VТ2) в открытом состоянии, независимо от состояния ключевых транзисторов (VТ1). Существенно лучшими показателями обладает инвертор КМДП логики (рис. 3.4, а), у которого нагрузочный транзистор VT2 включается и выключается в противофазе с транзистором VТ1. Для упрощения схемы управления удобно использовать транзисторы VТ1 и VТ2 с разными типами проводимости каналов. Это позволяет соединить их затворы между собой и управлять однополярными импульсами. Рассмотрим принцип действия инвертора.

Если на входе низкий уровень напряжения Uвх=U0вх, то открыт р-канальный транзистор VТ2, а n-канальный VT1 закрыт. Выходное напряжение соответствует логической 1 (Uвых=U1вых»Uп). Причем это напряжение поддерживает транзистор VT2 в открытом состоянии. Если на входе появляется высокий уровень напряжения (Uвх=U1вх»Uп), то транзистор VТ1 открывается, а VТ2 закрывается. Выходное напряжение близко к нулю (Uвых=U0вых»0)

Современные КМДП элементы допускают работу с напряжениями питания, изменяющимися в широких пределах (3 ... 15 В).

Очевидно, что в статическом режиме потребление тока данным элементом равно нулю. Лишь в момент переключения потребляется ток, определяемый в основном процессами перезаряда емкости нагрузки. Мощность, потребляемая элементом, растет пропорционально частоте переключения.

При напряжении Uп = 5 В элементы КМДП обладают совместимостью с элементами ТТЛ логики, превосходя последние по помехоустойчивости(Uпом»Uп/3).

На рис. 3.4,б изображен логический элемент ИЛИ-НЕ, работающий на том же принципе, что и рассмотренный КМДП инвертор.

Для того чтобы всегда можно было обеспечить большое управляемое сопротивление нагрузки, когда любое из входных напряжений будет иметь высокий уровень, соответствующее число канальных транзисторов включается последовательно. Несмотря на то, что при этом выходное сопротивление элемента в состоянии логической 1 возрастает, выходное напряжение логической 1 остается близким к напряжению источника питания Uп, так как в стационарном режиме ток не течет. Если нагрузочные транзисторы по выходу соединить параллельно, а каналы входных транзисторов соединить последовательно, то получится логический элемент, выполняющий операцию И-НЕ, представленный на рис. 3.4, в.

Как известно, МДП транзисторы чувствительны к наведенным электростатическим нарядам. Чтобы избежать пробоя МДП транзисторов, в современных ИС предусматривается встроенная защита с помощью диодов.

Логические элементы семейства И2Л появились позднее других и очень перспективны для интегрального исполнения. По существу, они являются модификацией схем ТЛНС, у которых вместо базовых и нагрузочных сопротивлений используются инжекторы: транзисторы в роли генераторов тока. Для реализации операции И па входе элемента И2Л включают диоды Шотки. Базовый элемент семейства И2Л, выполняющий операцию И-НЕ, показан на рис. 3.5. Как видно, базовый элемент семейства И2Л очень похож на элемент семейства ДТЛ, у которого на входе обычные диоды заменены диодами Шотки. Особенностью элементов семейства И2Л является широкое использование многоколлекторных транзисторов.

Рисунок 3.5

Принцип действия элемента И2Л аналогичен принципу действия элемента ДТЛ. Здесь базовый ток выходного транзистора VT2 обеспечивается выходной цепью р-n-р транзистора (VТ1), работающего в режиме генератора постоянного тока. Такая комбинация р-n-р и n-р-n транзисторов, реализуемая с помощью специального технологического процесса, занимает на кристалле очень малую площадь.

Ток, инжектируемый транзистором VT1, может меняться в широких пределах применительно к различным потребностям. Чем больше его величина, тем меньше среднее время задержки.