При синтезе систем связи с частотным разделением канала (с ЧРК) делаются следующие операции:

1. Расчет области частот среды распространения (в радиоаппаратуре - отведенная полоса частот, в кабельных линиях связи – это полоса частот от минимально разрешенной до максимально разрешенной для данной аппаратуры, для оптоволоконных линий – это окно прозрачности 1.55 мкм.).

2. Формирование группового сигнала (из канальных сигналов).

Групповой сигнал формируется из элементов телефонных каналов (0.3 – 3.4 кГц).

Из анализа работы систем связи с частотным разделением каналов виден существенный недостаток:

сложность формирования группового сигнала.

Вопрос - формирование N-канального сигнала.

При серийном производстве LC-фильтров настройка каждого происходит индивидуально. В связи с внедрением цифровых фильтров проблема выделения боковых частот существенно упрощается.

В настоящее время используются трансмультиплексоры, которые являются сложными цифровыми фильтрами, работающими в реальном масштабе времени.

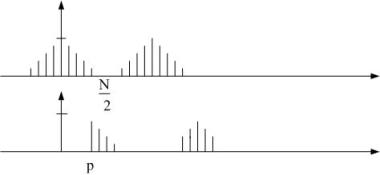

При формировании группового сигнала надо исходный спектр сигнала сдвинуть на p-тактовых интервалов в правую сторону.

![]()

![]()

![]()

![]()

При сдвиге вправо на p-тактовых интервалов надо домножить исходный сигнал на две составляющие:

![]()

Данный алгоритм выигрывает по сравнению с известными аналоговыми способами формирования нижней и верхней области частот. Структура преобразования проще и легче перестраиваема. Вся перестройка в замене p.

Эта операция переноса спектра является умножением (разложением) сигнала на синфазную и квадратурную составляющую.

Литература:

Маркин С. “Цифровые сигнальные процессы”.

Цифровые сигнальные процессы.

Этапы развития можно разбить:

1. разработка сигнального процессора МПД 7720 (для синтеза устройств преобразования сигналов)

2. ТМS3301, ТМS 3302

3. ТМS 3303 за 2 мкс., АДSP-21.

Обработка сигналов для радиотелефонов осуществляется с помощью МП DSP.

DSP используется при синтезе так называемых модемов (устройств стыков между ПЭВМ и существующей сетью локальных или глобальных), DSP используется при синтезе трансмультиплексоров.

Сравнительная таблица различных типов DSP.

| возможности | 21.01 | 21.03 | 21.05 | 21.11 | 21.

MSP50 |

21.61

21.62 |

21.63

21.64 |

21.71

21.73 |

21.72 | 21.15 | 21.81 |

| Память

программ RAM |

2кБай-

та |

2к | 1к | 2к | 2к | - | - | 2к | 2к | 1к | 16к |

| память пр-м

неперест-мая ROM |

- | - | - | - | - | 8к | 4к | - | 8к | - | - |

| память дан-ных RAM | 1к | 1к | 0.5к | 1к | 1к | 0.5к | 0.5к | 2к | 2к | 0.5к | 16к |

| наличие

таймера |

+ | + | + | + | + | + | + | + | + | + | + |

| послед.порт “0”многокан. | + | + | - | + | + | + | + | + | + | + | + |

| посл.порт”1” | + | + | + | + | + | + | + | + | + | + | + |

| порт XOTин-терфейса | + | + | + | + | |||||||

| порт ПДП | + | ||||||||||

| режим низ-кого энерго-потребления | + | + | + | + | |||||||

| аналог. Ин-терфейс | + | ||||||||||

| макс. F,МГц | 20 | 10.24 | 13.82 | 20 | 20 | 18.67;

10.24 |

18.63;

10.24 |

18.67;

10.24 |

18.67 | 20 | 18.67 |

| длина цикла,

нс |

50 | 97.6 | 72.3 | 50 | 50 | 80;

97.6 |

80;

97.6 |

30;50 | 30 | 50 | 30 |

| Напряжение питания,В | 5 | 3.3 | 5 | 5 | 5 | 5;3.3 | 5;3.3 | 5;3.3 | 5 | 5 | 5 |

ПДП - прямой доступ к памяти – это режим в многопроцессорной системе, когда требуется из верхнего звена считать данные из более нижнего звена с отключением процессора низового звена.

Стык (согласование) с вышестоящим процессором, когда функции периферийного устройства выполняют выше названные.

В любом процессоре DSP три режима работы:

1. активный, работает на полную мощность;

2. режим приема команд скорость обработки сигналов уменьшается

3. режим молчания (при самом экономном энергопотреблении).

Из анализа совокупности характеристик наиболее перспективным является процессор 21 MSP 50 (ADSP-21-MSP-50) , наиболее быстродействующим является ADSP-2181.

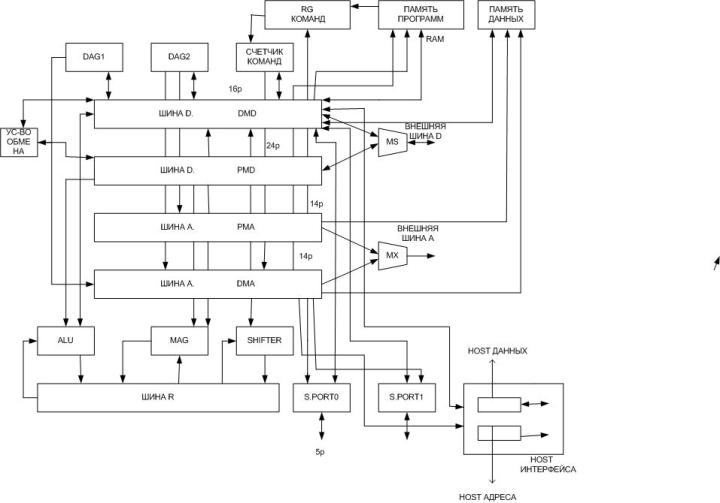

Структурная схема сигнальных процессоров.

Стандартна для всех, отличие одной структуры от другой – в наличии или в отсутствии каких-то составных блоков. Для уменьшения времени выполнения в структуре предусмотрены два генератора в адресном пространстве DAG1 и DAG2 (аппаратный накопитель умножителей), позволяют за один такт умножить два 40-разрядных числа и прибавить полученное произведение к предыдущему результату.

Блок MAC – умножитель накопителей.

АЛУ – арифметическое логическое устройство, позволяет произвести сложение либо вычитание

логич.+, *, сложение по модулю 2.

Для обмена с внешними устройствами существуют специальные порты (SPORT) , у отдельных процессоров специальных портов несколько: последовательные “0”,”1” и последовательный XOT интерфейс.

В каждом из перечисленных выше процессоров имеется возможность организации памяти барабанного типа SHIFTER.

Устройство обмена позволяет переслать данные с одной шины на другую (с шины DMD на PMD и наоборот), согласовывать разный формат данных (PMD (24 разряда) и DMD (16 разрядов)).

Процессор в отличие от существующих процессоров имеет 5 шин:

Шина DMD-datamemorydata, вводятся исходные данные или окончательные результаты.

Шина PMD – шина инструкций programmemorydata, может использоваться и для данных, подлежащих вычислению (для повышения производительности).

Шина адресов PMA – programmemoryaddress, при начальной загрузке процессора, а также при чтении рабочей программы из памяти программ RAM.

DMA – datamemoryaddress, предназначена для чтения памяти данных ROM, для организации обмена по последовательному интерфейсу через SPORT0 и SPORT1.

Согласно рекомендации МККТТ последовательный обмен производится с помощью телеграфного 5р.кода, может вводиться асинхронно.

ALU совместно с аппаратным умножителем МАG и АЗУ барабанного типа SHIFTER образует 5 шину: шину R, позволяет переслать промежуточные результаты вычислений или из ALU в MAG или наоборот; либо с задействованием SHIFTER, при этом операции происходят бок о бок. Для построения иерархической системы связи, когда DSP связь осуществляется через HOST интерфейс (является устройством, кроме HOST интерфейса имеет возможность связаться с шиной адреса через два мультиплексора).

В HOST интерфейсе используется параллельная RG защелка. Такая защелка позволяет синхронизировать информацию.

Надо предусмотреть стандартное устройство ввода /вывода.

ADSP

Сигнал Reset поступает программно от старшей по иерархии программной сетки. RG команд и счетчик обнуляются и указывают на нулевую ячейку памяти программ, где указан номер строки, с которой начинается первоначальная загрузка.

Установка всех составных блоков в исходное состояние.

Для того, чтобы разделить поток данных и поток инструкций (команд), используются 4 шины. Сигналы с одной шины в процессе обработки могут пересылаться на другую шину по специальной команде. Процесс разделения шин позволил существенно увеличить скорость обработки, для этой операции служат генераторы DAG1 и DAG2. Адресация в ОЗУ возможна в двух вариантах:

1. абсолютная адресация

2. косвенная адресация

Для уменьшения времени на выполняемую команду DAG1 и DAG2 автоматически инициируется.

Структура построения микропроцессорного комплекса.

Как и любая вычислительная система, сигнал. М.П.комплекс содержит три составляющие:

1. центральный процессорный элемент

2. постоянное запоминающее устройство первоначальной инициализации и хранения памяти программ

3. операторное запоминающее устройство

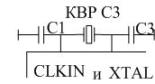

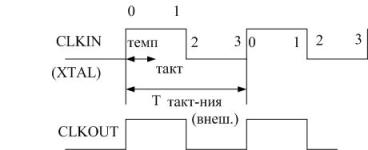

CLKIN и XTAL предназначены для подключения внешнего кварцевого резонатора, либо для подключения внешней тактовой частоты.

В случае, если используется внешняя тактовая частота, то тактовые импульсы подаются CLKIN, а вход XTAL остается свободным. Внутри центрального процессорного элемента происходит умножение тактовой частоты на 4. Совместно с тактовой частотой производится синхронизированный вывод выполняемых операций на выходе CLKOUT.

Вход RESET – вход сброса аппаратной реализации, по этому входу МПК сбрасывается в исходное состояние при первоначальном включении.

Вход MMAP – memory map control signal.

MMAP – вход для программного сброса, происходит обнуление сигналов от более старшего МП комплекта.

SPORT1 и SPORT0 – два последовательных устройства ввода/вывода, которые позволяют производить не только обмен данных, но и делать прерывание, более старшие прерывания IRQ-0, следующие IRQ-4.

В отличие от известных управл.процессоров прерывание может производиться как с последующего устройства ввода/вывода, так и ADSP. В случае если процессор работает в многопроцессорной системе, то используется постпроцессор.

а) отладка рабочей программы, тогда вместо постпроцессора используется ЭВМ

б) используется многопроцессорная система - сигнал.процессор (ближнего и дальнего уровня)

Центральный процессорный элемент имеет три шины: ША(14р.), ШД(24р.), Ш Управления (включает три сигнала, разделенные во времени:![]() ); определяет порядок работы внешней памяти.

); определяет порядок работы внешней памяти.

Если ![]() 0, то производится обращение памяти к первоначальной инициализации

0, то производится обращение памяти к первоначальной инициализации

![]()

Для того, чтобы прочесть в памяти данных, вырабатывается сигнал![]() , а записать –

, а записать –![]() .

.

При первоначальной инициализации ввод производится по 4 байта, при этом в начале первый байт.

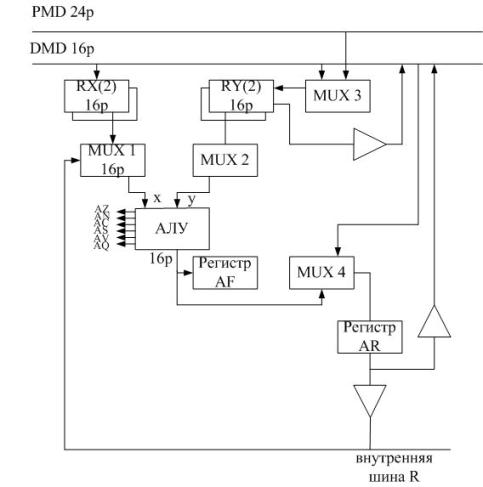

Структура АЛУ.

АЛУ – самостоятельный блок, входящий в процессор ATSP, позволяет выполнить:

1. R=x+y 9. R=x XQR y

2. R=x-y 10. R=PASS x

3. R=y-x 11. R=PASS y

4. R=x+y+CI 12. R=NOT x

5. R=x-y-CI+1 13. R=NOT y

6. R=y-x-CI+1 14. R=x+1

7. R=x OR y 15. R=y+1

8. R=x AND y

АЛУ состоит из блока RGx (2![]() 16 раз.), блока RGy (2

16 раз.), блока RGy (2![]() 16 раз.). Каждый из этих RG обрамлен мультиплексором, с его помощью сигнал может приниматься с двух направлений.

16 раз.). Каждый из этих RG обрамлен мультиплексором, с его помощью сигнал может приниматься с двух направлений.

Первый блок RGRx совместно с мультиплексором MX1 позволяет выдать на вход сигнал либо с выхода Rx, либо с внутренней шины R.

MUX2 позволяет сделать аналогичные операции с выхода Ry и AR.

MU3 позволяет объединить шины DMD и PMD для записи второго операнда y, обе шины имеют разную разрядность (16 р. и 24 р.). Согласование разрядности происходит автоматически. Для выбора RGRy существуют два банка данных, для выбора нулевого банка данных надо указать команду MSTAX0.

При выполнении арифметических и логических операций формируются признаки:

1. AZ - признак нуля

2. AN- признак отрицательного результата

3. AC - признак переноса из 16 в 17 раз

4. AS - признак знака

5. AV - признак переполнения

6. AQ- признак частного

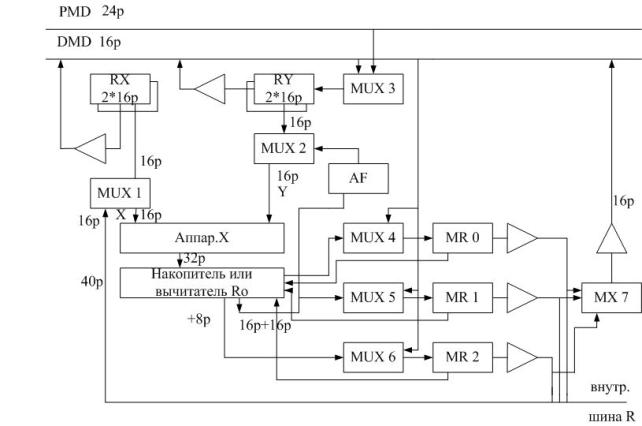

Структура умножителя MAC.

1. R=xy

2. R=MR+xy

3. R=MR-xy

4. MR=0

MAC состоит:

1. блок 2![]() 16р. RG

16р. RG

для согласования 16р MR0 – MR1

MUX1 нужен для коммутации

MUX2

MUX3 коммутирует входные сигналы либо с шины DMD, либо с PMD.

MUX4-6 коммутирует на входы RGMR0-MR2, либо с выхода накопителя (вычитателя) R0-R2, либо с шины DMD. Специально ориентирован на временные свертки.

Два банка Rx и Ry постоянно меняются местами при вычислении свертки.

Список литературы

1. Гоноровский «Радиотехнические цепи и сигналы».

2. Голденберг Справочник по ЦОС.

3. Карташов «Основы теории дискретных сигналов и цифровых фильтров».

4. Робинер «Теория и применение ЦОС».

5. Ленг «Аналоговые и цифровые фильтры».

6. Антонию «Цифровые фильтры, анализ и проектирование».