3.3. Таблица векторов прерываний

3.1. Функции памяти

Память микропроцессорной системы выполняет функцию временного или постоянного хранения данных и команд. Объем памяти определяет допустимую сложность выполняемых системой алгоритмов, а также в некоторой степени и скорость работы системы в целом. Модули памяти выполняются на микросхемах памяти (оперативной или постоянной).

Информация в памяти хранится в ячейках, количество разрядов которых равно количеству разрядов шины данных процессора. Допустимое количество ячеек памяти определяется количеством разрядов шины адреса как 2N, где N – количество разрядов шины адреса. Чаще всего объем памяти измеряется в байтах независимо от разрядности ячейки памяти.

Используются также следующие более крупные единицы объема памяти:

- килобайт – 210 или 1024 байта (обозначается Кбайт),

- мегабайт – 220 или 1 048 576 байт (обозначается Мбайт),

- гигабайт – 230 байт (обозначается Гбайт),

- терабайт – 240 (обозначается Тбайт).

Например, если память имеет 65 536 ячеек, каждая из которых 16-разрядная, то говорят, что память имеет объем 128 Кбайт. Совокупность ячеек памяти называется обычно пространством памяти системы.

Для подключения модуля памяти к системной магистрали используются блоки сопряжения, которые включают в себя (рис. 3.1):

- дешифратор (селектор) адреса; селектор адреса как раз и определяет, какая область адресов пространства памяти отведена данному модулю памяти.

- схему обработки управляющих сигналов магистрали; схема управления вырабатывает в нужные моменты сигналы разрешения работы памяти (CS) и сигналы разрешения записи в память (WR).

- буферы данных; буферы данных передают данные от памяти к магистрали или от магистрали к памяти.

Рисунок 3.1 – Структура модуля памяти

Рисунок 3.1 – Структура модуля памяти

Оперативная память общается с системной магистралью в циклах чтения и записи, постоянная память – только в циклах чтения.

В пространстве памяти микропроцессорной системы обычно выделяются несколько особых областей, которые выполняют специальные функции:

- память программы начального запуска всегда выполняется на ПЗУ или флэш-памяти. Именно с этой области процессор начинает работу после включения питания и после сброса его с помощью сигнала RESET;

- память для стека или стек (Stack) – это часть оперативной памяти, предназначенная для временного хранения данных в режиме LIFO (Last In – First Out);

- таблица векторов прерываний. Под прерыванием в общем случае понимается не только обслуживание запроса внешнего устройства, но и любое нарушение последовательной работы процессора. Прерывание может быть программным, когда в программе используется команда перехода на какую-то подпрограмму, из которой затем последует возврат в основную программу. Любое прерывание обрабатывается через таблицу векторов(указателей) прерываний. В этой таблице в простейшем случае находятся адреса начала программ обработки прерываний, которые и называются векторами. Обычно таблица векторов прерываний располагается в начале пространства памяти (в ячейках памяти с малыми адресами). Адрес каждого вектора (или адрес начального элемента каждого вектора) представляет собой номер прерывания;

- память устройств, подключенных к системной шине – процессор получает возможность обращаться к внутренней памяти устройств ввода/вывода или каких-то еще подключенных к системной шине устройств, как к своей собственной системной памяти. Обычно для этого выделяется окно в пространстве памяти.

Все остальные части пространства памяти, как правило, имеют универсальное назначение. В них могут располагаться как данные, так и программы (конечно, в случае одношинной архитектуры). Иногда пространство памяти делится на сегменты с программно изменяемым адресом начала сегмента и с установленным размером сегмента. Использование сегментов позволяет защитить область программ или данных, но зато границы сегментов могут затруднять размещение больших программ и массивов данных.

Остановимся на проблеме разделения адресов памяти и адресов устройств ввода/вывода. Существует два основных подхода к решению этой проблемы:

- выделение в общем адресном пространстве системы специальной области адресов для устройств ввода/вывода; хорош тем, что при обращении к устройствам ввода/вывода процессор может использовать те же команды, которые служат для взаимодействия с памятью. Но адресное пространство памяти должно быть уменьшено на величину адресного пространства устройств ввода/вывода.

- полное разделение адресных пространств памяти и устройств ввода/вывода. Преимущество такого подхода состоит в том, что память занимает все адресное пространство микропроцессорной системы. Для общения с устройствами ввода/вывода применяются специальные команды. Так сделано, например, в персональных компьютерах. Но возможности взаимодействия с устройствами ввода/вывода в данном случае существенно ограничены по сравнению с возможностями общения с памятью.

3.2. Организация стека

Особенность стека по сравнению с другой оперативной памятью – это заданный и неизменяемый способ адресации.

При записи любого числа (кода) в стек число записывается по адресу, определяемому как содержимое регистра указателя стека, предварительно уменьшенное (декрементированное) на единицу (или на два, если 16-разрядные слова расположены в памяти по четным адресам). При чтении из стека число читается из адреса, определяемого содержимым указателя стека, после чего это содержимое указателя стека увеличивается (инкрементируется) на единицу (или на два). В результате получается, что число, записанное последним, будет прочитано первым, а число, записанное первым, будет прочитано последним. Такая память называется LIFO или памятью магазинного типа (например, в магазине автомата патрон, установленный последним, будет извлечен первым).

Принцип действия стека показан на рис. 3.2 (адреса ячеек памяти выбраны условно).

Рисунок 3.2 – Принцип работы стека

Рисунок 3.2 – Принцип работы стека

Пусть, например, текущее состояние указателя стека 1000008, и в него надо записать два числа (слова). Первое слово будет записано по адресу 1000006 (перед записью указатель стека уменьшится на два). Второе – по адресу 1000004. После записи содержимое указателя стека – 1000004. Если затем прочитать из стека два слова, то первым будет прочитано слово из адреса 1000004, а после чтения указатель стека станет равным 1000006. Вторым будет прочитано слово из адреса 1000006, а указатель стека станет равным 1000008. Все вернулось к исходному состоянию. Первое записанное слово читается вторым, а второе – первым.

Необходимость такой адресации становится очевидной в случае многократно вложенных подпрограмм. Пусть, например, выполняется основная программа, и из нее вызывается первая подпрограмма. Если нам надо сохранить значения данных и внутренних регистров основной программы на время выполнения подпрограммы, мы перед вызовом подпрограммы сохраним их в стеке (запишем в стек), а после ее окончания извлечем (прочитаем) их из стека. Если же из первой подпрограммы вызывается вторая подпрограмма, то ту же самую операцию мы проделаем с данными и содержимым внутренних регистров первой подпрограммы. Понятно, что внутри второй подпрограммы крайними в стеке (читаемыми в первую очередь) будут данные из первой подпрограммы, а данные из основной программы будут глубже. При этом в случае чтения из стека автоматически будет соблюдаться нужный порядок читаемой информации.

В системе команд любого процессора для обмена информацией со стеком предусмотрены специальные команды записи в стек (PUSH) и чтения из стека (POP). Можно также хранить в стеке и данные, для того чтобы удобнее было передавать их между программами и подпрограммами. В общем случае, чем больше область памяти, отведенная под стек, тем больше свободы у программиста и тем более сложные программы могут выполняться.

3.3. Таблица векторов прерываний

В случае аппаратных прерываний номер прерывания или задается устройством, запросившим прерывание (при векторных прерываниях), или же задается номером линии запроса прерываний (при радиальных прерываниях).

Процессор, получив прерывание, заканчивает выполнение текущей команды и обращается к памяти в область таблицы векторов прерываний, в ту ее строку, которая определяется номером запрошенного прерывания. Затем процессор читает содержимое этой строки (код вектора прерывания) и переходит в адрес памяти, задаваемый этим вектором. Начиная с этого адреса в памяти должна располагаться программа обработки прерывания с данным номером. В конце программы обработки прерываний обязательно должна располагаться команда выхода из прерывания, выполнив которую, процессор возвращается к выполнению прерванной основной программы. Параметры процессора на время выполнения программы обработки прерывания сохраняются в стеке.

Рисунок 3.3 – Упрощенный алгоритм обработки прерывания

Рисунок 3.3 – Упрощенный алгоритм обработки прерывания

Пусть, например, процессор (рис. 3.3) выполнял основную программу и команду, находящуюся в адресе памяти 5000 (условно). В этот момент он получил запрос прерывания с номером (адресом вектора) 4. Процессор заканчивает выполнение команды из адреса 5000. Затем он сохраняет в стеке текущее значение счетчика команд (5001) и текущее значение PSW. После этого процессор читает из адреса 4 памяти код вектора прерывания. Пусть этот код равен 6000. Процессор переходит в адрес памяти 6000 и приступает к выполнению программы обработки прерывания, начинающейся с этого адреса. Пусть эта программа заканчивается в адресе 6100. Дойдя до этого адреса, процессор возвращается к выполнению прерванной программы. Для этого он извлекает из стека значение адреса (5001), на котором его прервали, и бывшее в тот момент PSW. Затем процессор читает команду из адреса 5001 и дальше последовательно выполняет команды основной программы.

Прерывание в случае аварийной ситуации обрабатывается точно так же, только адрес вектора прерывания (номер строки в таблице векторов) жестко привязан к данному типу аварийной ситуации.

Программное прерывание тоже обслуживается через таблицу векторов прерываний, но номер прерывания указывается в составе команды, вызывающей прерывание.

3.4. Сегментирование памяти

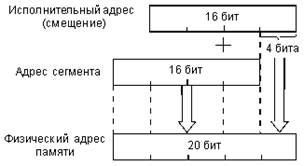

Говоря об адресации, нельзя обойти вопрос о сегментировании памяти, применяемой в некоторых процессорах, например в процессорах IBM PC-совместимых персональных компьютеров. В процессоре Intel 8086 сегментирование памяти организовано следующим образом.

Вся память системы представляется не в виде непрерывного пространства, а в виде нескольких кусков – сегментов заданного размера (по 64 Кбайта), положение которых в пространстве памяти можно изменять программным путем.

Для хранения кодов адресов памяти используются не отдельные регистры, а пары регистров:

- сегментный регистр определяет адрес начала сегмента (то есть положение сегмента в памяти);

- регистр указателя (регистр смещения) определяет положение рабочего адреса внутри сегмента.

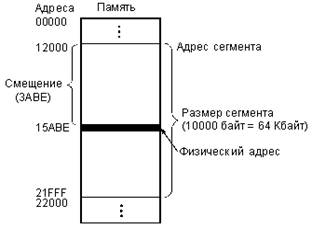

При этом физический (20-разрядный) адрес памяти, выставляемый на внешнюю шину адреса, образуется так, как показано на рис. 3.4, то есть путем сложения смещения и адреса сегмента со сдвигом на 4 бита. Положение этого адреса в памяти показано на рис. 3.5.

|

|

|

|

Рисунок 3.4 – Формирование физического адреса памяти из адреса сегмента и смещения |

Рисунок 3.5 – Физический адрес в сегменте (все коды – шестнадцатеричные) |

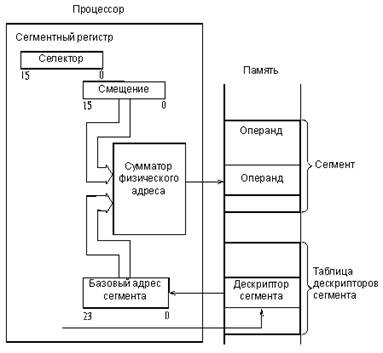

Применяются и более сложные методы сегментирования памяти. Например, в процессоре Intel 80286 в так называемом защищенном режиме адрес памяти вычисляется в соответствии с рис. 3.6.

Рисунок 3.6 – Адресация памяти в защищенном режиме процессора Intel 80286

В сегментном регистре в данном случае хранится не базовый (начальный) адрес сегментов, а коды селекторов, определяющие адреса в памяти, по которым хранятся дескрипторы (то есть описатели) сегментов. Область памяти с дескрипторами называется таблицей дескрипторов. Каждый дескриптор сегмента содержит базовый адрес сегмента, размер сегмента (от 1 до 64 Кбайт) и его атрибуты.

Таким образом, на сумматор, вычисляющий физический адрес памяти, подается не содержимое сегментного регистра, как в предыдущем случае, а базовый адрес сегмента из таблицы дескрипторов.

Сегментирование позволяет выделить в памяти один или несколько сегментов для данных и один или несколько сегментов для программ. Переход от одного сегмента к другому сводится всего лишь к изменению содержимого сегментного регистра.

3.5. Режимы работы памяти

3.5.1. Реальный режим

В реальном режиме (Real Mode) МП работает как очень быстрый 8086 с возможностью использования 32-битных расширений.

Имеется две фиксированные области в памяти, которые резервируются в режиме реальной адресации:

- область инициализации системы,

- область таблицы прерываний.

3.5.2. Режим системного управления

В новых поколениях МП Intel появился еще один режим работы с памятью – режим системного управления (System Management Mode) с его помощью прозрачно даже для операционной системы на уровне BIOS реализуются функции энергосбережения.

Режим системного управления предназначен для выполнения некоторых действий с возможностью их полной изоляции от прикладного программного обеспечения и даже от операционной системы. МП переходит в этот режим только аппаратно.

3.5.3. Защищенный режим

Основным режимом работы МП является защищенный режим (Protected Mode). Ключевые особенности защищенного режима:

- виртуальное адресное пространство;

- защита;

- многозадачность.

В защищенном режиме программа оперирует с адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называется виртуальным.

Размер виртуального адресного пространства программы может превышать емкость физической памяти и достигать 64 Тбайт.

Преобразование логического адреса в физический происходит в два этапа:

- сначала блок управления сегментами выполняет трансляцию адреса в соответствии с сегментированной моделью памяти, получая линейный адрес,

- затем блок страничного преобразования выполняет разбиение на страницы, преобразуя линейный адрес в физический.

В рамках сегментированной модели адресации для программы память представляется группой независимых адресных блоков, называемых сегментами.

Механизм сегментации обеспечивает превосходную защиту, но он не очень удобен для реализации виртуальной памяти (подкачки). В дескрипторе сегмента есть бит присутствия, по нему процессор определяет, находится ли данный сегмент в физической памяти или на внешнем запоминающем устройстве(на винчестере). В последнем случае генерируется исключение, обработчик которого может подгрузить сегмент с жесткого диска в память.

Неудобство заключается в том, что различные сегменты могут иметь различную длину. Этого можно избежать, если механизм подкачки реализовывать на основе страничного преобразования. Особенностью этого преобразования является то, что процессор в этом случае оперирует с блоками физической памяти равной длины (4 Кбайт) – страницами.

Встроенные средства переключения задач обеспечивают многозадачность в защищенном режиме. В качестве задачи может исполняться прикладная программа, сервис операционной системы, ядро операционной системы, обработчик прерывания или исключения и т.п.

Среда задачи состоит из содержимого регистров МП и всего кода с данными в пространстве памяти. МП способен быстро переключаться из одной среды выполнения в другую, имитируя параллельную работу нескольких задач.

Задачу составляют два компонента:

- адресное пространство задачи; в нее входят доступные ей сегменты кода, данных и стека. Если используется механизм привилегий, то каждой задаче должны быть предоставлены сегменты стека для всех используемых уровней привилегий.

- сегмент состояния задачи (Task State Segment – TSS). Сегмент состояния задачи хранит состояние регистров (контекст) процессора:

- состояние сегментных регистров (селекторы сегментов, формирующие адресное пространство задачи);

- состояние регистров общего назначения;

- состояние регистра флагов (EFLAGS);

- указатель очередной команды (EIP);

- значение регистра CR3 (PDBR);

- значение регистра LDTR.

Каждая задача идентифицируется селектором соответствующего ей TSS. Операционная система может предусматривать для каждой задачи свое линейное адресное пространство.

В защищенном режиме процессор обеспечивает определенные механизмы защиты на основе сегментации и на основе страничного преобразования. Механизмы защиты позволяют ограничивать доступ к определенным сегментам или страницам при помощи уровней привилегий.

Механизм защиты обеспечивает соответствие любой ссылки на ячейки памяти определенным условиям. Все проверки выполняются до начала цикла обращения к памяти. Нарушение любого условия приводит к генерации исключения. Проверки выполняются параллельно с формированием адреса и поэтому не ухудшают производительность процессора.

В защищенном режиме нет способа отключить механизм защиты. Контроль пределов и типов сегментов обеспечивает целостность сегментов кода и данных. Программа не имеет права обратиться к виртуальной памяти, выходящей за предел того или иного сегмента. Программа не имеет права обратиться к сегменту данных как к коду, и наоборот.

3.6. Устройства ввода/вывода

Устройства ввода/вывода обмениваются информацией с магистралью по тем же принципам, что и память.

Наиболее существенное отличие с точки зрения организации обмена состоит в том, что модуль памяти имеет в адресном пространстве системы много адресов (до нескольких десятков миллионов), а устройство ввода/вывода обычно имеет немного адресов (обычно до десяти), а иногда и всего один адрес. Но модули памяти системы обмениваются информацией только с магистралью, с процессором, а устройства ввода/вывода взаимодействуют еще и с внешними устройствами.

Объединяют все устройства ввода/вывода общие принципы обмена с магистралью и, соответственно, общие принципы организации узлов, которые осуществляют сопряжение с магистралью.

Упрощенная структура устройства ввода/вывода (точнее, его интерфейсной части) приведена на рис. 3.7. Она обязательно содержит:

- схему селектора адреса;

- схему управления для обработки стробов обмена;

- буферы данных.

Самые простейшие устройства ввода/вывода выдают на внешнее устройство код данных в параллельном формате и принимают из внешнего устройства код данных в параллельном формате. Такие устройства ввода/вывода часто называют параллельными портами ввода/вывода.

Рисунок 3.7 – Структура простейшего устройства ввода/вывода

Рисунок 3.7 – Структура простейшего устройства ввода/вывода

Входной порт (порт ввода) в простейшем случае представляет собой параллельный регистр, в который процессор может записывать информацию. Выходной порт (порт вывода) обычно представляет собой просто однонаправленный буфер, через который процессор может читать информацию от внешнего устройства. Именно такие порты показаны для примера на рис. 3.7. Порт может быть и двунаправленным (входным/выходным).

При обращении со стороны магистрали селектор адреса распознает адрес, приписанный данному устройству ввода/вывода. Входной буфер данных обеспечивает электрическое согласование шины данных с этим устройством (буфер может и отсутствовать). Данные из шины данных записываются в регистр и выдаются на внешнее устройство. Выходной буфер данных передает входные данные с внешнего устройства на шину данных магистрали в цикле чтения из порта.

Более сложные устройства ввода/вывода (устройства сопряжения) имеют в своем составе внутреннюю буферную оперативную память и даже могут иметь микроконтроллер, на который возложено выполнение функций обмена с внешним устройством.

Каждому устройству ввода/вывода отводится свой адрес в адресном пространстве микропроцессорной системы. Дублирование адресов должно быть исключено, за этим должны следить разработчик и пользователь микропроцессорной системы.

В составе микропроцессорных систем, как правило, выделяются три специальные группы устройств ввода/вывода:

- устройства интерфейса пользователя (ввода информации пользователем и вывода информации для пользователя);

- устройства ввода/вывода для длительного хранения информации;

- таймерные устройства.

К устройствам ввода для интерфейса пользователя относятся контроллеры клавиатуры, тумблеров, отдельных кнопок, мыши, трекбола, джойстика и т.д. К устройствам вывода для интерфейса пользователя относятся контроллеры светодиодных индикаторов, табло, жидкокристаллических, плазменных и электронно-лучевых экранов и т.д.

Устройства ввода/вывода для длительного хранения информации обеспечивают сопряжение микропроцессорной системы с дисководами (компакт-дисков или магнитных дисков), а также с накопителями на магнитной ленте.

Таймерные устройства отличаются от других устройств ввода/вывода тем, что они могут не иметь внешних выводов для подключения к внешним устройствам. Эти устройства предназначены для того, чтобы микропроцессорная система могла выдерживать заданные временные интервалы, следить за реальным временем, считать импульсы и т.д. В основе любого таймера лежит кварцевый тактовый генератор и многоразрядные двоичные счетчики, которые могут перезапускать друг друга.

Еще один важный класс устройств ввода/вывода – это устройства для подключения к информационным сетям (локальным и глобальным). Эти устройства распространены не так широко, как устройства трех перечисленных ранее групп, но их значение с каждым годом становится все больше. Сейчас средства связи с информационными сетями вводятся иногда даже в простые контроллеры.