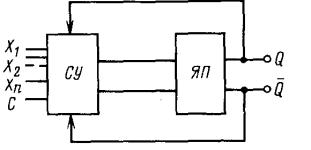

Общие сведения. Помимо логических элементов, реализующих основные логические операции, в цифровой технике широко используются в качестве базовых элементов ячейки памяти на основе разнообразных триггеров. Обобщенная модель триггера показана на рис. 3.6. Очевидно, любой триггер состоит из схемы управления (СУ) и бистабильной ячейки памяти (ЯП). Триггеры имеют входы управляющих сигналов Х1, Х2,…Хn два взаимоинверсных выхода Q и  , а также могут иметь вход синхронизации С.

, а также могут иметь вход синхронизации С.

В общем случае к триггерам относят устройства, имеющие два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации сигналов на управляющие входы и

Рисунок 3.6

сохраняются в течение заданного времени после окончания действия этих сигналов. Триггеры способны хранить двоичную информацию (состояния «О» и «1») после окончания действия входных импульсов. Это свойство обусловлено тем, что устройством управляют не только внешние сигналы, но и сигналы обратной связи самого триггера.

По функциональному признаку, определяющему поведение триггера при воздействии сигнала управления и способа управления, триггеры подразделяют на следующие типы:

RS-триггеры, имеющие два управляющих входа: S (set— установка) и R (reset—сброс); D-триггеры (D—delay—задержка), имеющие один информационный вход;

Т—триггеры (T—time—время, характеризующее внутреннюю задержку), переключающиеся в противоположное состояние с приходом каждого очередного входного импульса.

Часто Т-триггеры называют триггерами со счетным запуском. Иногда Т-триггеры обозначают MS. Это отражает то, что каждый из них состоит из двух RS-триггеров, один из которых является основным (М—master—хозяин), а другой—вспомогательный (S—slave—раб);

JK—универсальные триггеры, имеющие управляющие входы J (J—-jump—прыжок, переброс) и К (keep—держать, сохранять) и допускающие установку выходных уровней при наличии сигнала на входе синхронизации С.

По способу управления триггеры подразделяют на асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах переключение производится только при наличии разрешающего, тактирующего импульса на входе синхронизации.

В зависимости от типа используемых ячеек памяти триггеры подразделяются на статические, статико-динамические и динамические. Первые два типа реализуются на основе логических элементов НЕ, ИЛИ-

НЕ, И-НЕ, а последний на основе МДП транзисторов.

В зависимости от типа базовых логических элементов реализуются триггеры с различными параметрами: быстродействием, потребляемой мощностью, нагрузочной способностью и др.

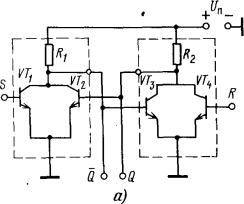

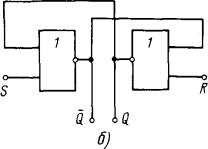

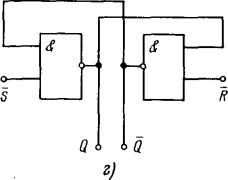

RS-триггер. Простейшим триггером является асинхронный RS-триггер. Такой триггер нетрудно реализовать на основе двух логических элементов ИЛИ-НЕ (рис. 3.7, а) или И-НЕ (рис. 3.7, в).

Как видно из рассмотрения принципиальных схем, основу триггеров составляют два инвертора, связанные между собой взаимными перекрестными связями. Эти связи обусловливают в процессе переключения возникновение положительной обратной связи, способствующей повышению быстродействия и надежности работы схемы.

Рисунок 3.7.

При наличии логической 1 на выходе одного инвертора на выходе другого поддерживается логический 0. Необходимые уровни напряжения на выходе издаются схемой управления, которая при использовании логических элементов семейства ТЛНС (см. рис. 3.7, а) образована транзисторами VT1 и VT2, а при использовании элементов семейства ТТЛ (см. рис. 3.7, в) образована эмиттерными переходами транзисторов VT1 и VT2. Триггеры, реализованные на основе логических элементов ИЛИ-НЕ, работают в положительной логике, а реализованные на основе логических элементов И-НЕ работают в отрицательной логике. Для работы в положительной логике схема управления последних усложняется добавлением двух инверторов.

Уровни напряжений на обоих выходах триггера различны и одновременно изменяются на противоположные при работе устройства управления. Поэтому на условном обозначении триггера (см. рис. 3.7, б, г) один из выходов обозначен Q, а второй—через  (факт инверсии отражается кружком на стороне прямоугольника). Выход Q считается главным: значениями Q характеризуют состояние триггера в целом.

(факт инверсии отражается кружком на стороне прямоугольника). Выход Q считается главным: значениями Q характеризуют состояние триггера в целом.

Уравнение состояний RS-триггера имеет вид  Здесь индексами n и n+1 обозначены значения величины Q до и после поступления управляющих сигналов. Используя это уравнение, можно определить возможные состояния триггера при разных наборах управляющих сигналов:

Здесь индексами n и n+1 обозначены значения величины Q до и после поступления управляющих сигналов. Используя это уравнение, можно определить возможные состояния триггера при разных наборах управляющих сигналов:

если S = 0, R = 0, то

, т.е. триггер сохраняет прежнее состояние;

если S = 0, R = 1, то

, т.е триггер по основному выходу находится в состоянии логического ;

если S = 1, R = 0, то

, т.е. триггер по основному выходу находится в состоянии логической 1;

если S = 1 и R = 1, то триггер находится в неопределенном состоянии Х, (т.е. с равной вероятностью может находиться в любом из устойчивых состояний Q = 1 или Q = 0), поэтому такой набор является запрещенным: нельзя одновременно подавать на триггер противоположные команды S (установить 1) и R (установить 0).

Интегральные триггеры. Наряду с простыми логическими элементами в состав серий ЦИС входят триггеры различных типов и устройства на их основе: регистры, счетчики, сумматоры и др. Данные об основных типах интегральных триггеров сведены в табл. 3.3.

Наибольшей универсальностью среди триггеров обладает JK-триггер Он работает как RS-триггер, причем в отличие от RS-триггеров здесь допустимо, чтобы оба управляющих сигнала были равны 1.

Если управляющие сигналы J и К равны 1, то JK-триггер работает как T-триггер. При подаче на вход С синхронизирующего импульса триггер будет работать в режиме делителя на 2. Этот режим используется при построении последовательных счетчиков и делителей частоты любой сложности.

Если на информационные входы J и К подавать противофазные логические сигналы, то триггер будет работать в режиме синхронной записи информации. При подаче тактового импульса на вход С эта информация появляется на выходе, т. е. сдвигается в следующую ячейку Такой режим используется при построении сдвигающих регистров, распределителей импульсов, синхронных.

Интегральные JK-триггеры часто имеют несколько управляющих J, К входов, что расширяет его функциональные возможности и позволяет экономить внешние логические элементы. С помощью указанных входов триггер можно установить в определенное состояние независимо от тактового импульса. Поэтому эти входы получили названия предустановки и стирания.

Квазистатические и динамические триггеры. В квазистатических и динамических триггерах используют свойство МДП транзистора сохранять заряд на паразитной емкости затвора в течение определенного времени.

Таблица 3.

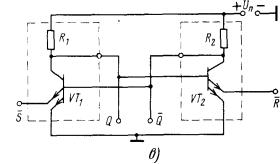

Рисунок 3.8

Квазистатические триггеры в отличие от динамических не требуют так называемого «тактового питания» в период хранения информации. При записи информации тактовое питание необходимо, оно осуществляется тактовыми импульсами, имеющими длительность, меньшую, чем постоянная времени заряда и разряда паразитных емкостей затворов МДП транзисторов схемы. По сравнению со схемами статического типа квазистатические и динамические схемы триггеров позволяют в 2—3 раза уменьшить число используемых МДП транзисторов.

В динамических триггерах по истечении времени хранения информация теряется. Для сохранения информации необходимо ее периодическое восстановление путем подачи последовательности внешних импульсов, период которых Т меньше времени хранения информации t. Эти импульсы одновременно выполняют функции синхронизации. В зависимости от числа последовательностей синхроимпульсов различают двух- и четырехфазные динамические элементы.

Характерной особенностью цифровых устройств на основе динамических триггеров является то, что синхронизация в них осуществляется путем подключения и отключения соответствующих элементов к цепи питания. При этом элементы потребляют мощность от источника питания не постоянно, а периодически в течение относительно коротких промежутков времени, когда производится переключение элементов или восстановление информации. В результате устройства на динамических элементах при низких частотах переключения потребляют существенно меньшую мощность, чем на основе статических триггеров. Поэтому динамические триггеры являются весьма перспективными элементами для БИС памяти. Рассмотрим принцип действия динамического триггера, пригодного для использования в качестве ячейки памяти БИС.

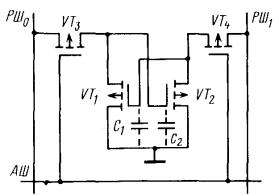

На рис. 3.8 изображена схема динамического триггера на основе двух инверторов VT1, VT3 и VT2, VТ4, с взаимными перекрестными связями. В триггере используются МДП транзисторы с каналом р-типа. Питание и синхронизация работы триггера производятся импульсными последовательностями, подаваемыми в разрядные шины РШ0 и РШ1 (в них потенциалы могут принимать значения –Un, 0 B). Хранение информации обеспечивается паразитными емкостями МДП транзисторов, для удобства обозначенными С1 и С2.

Для записи на адресную шину подают напряжение –Un, а на разрядные шины РШ1 и РШ0 подают уровни –Un и 0. Уровень –Un через ключ VT4 поступает на вход транзистора VT1 и открывает его. На затвор транзистора VT2 поступает уровень 0, и, следовательно, он закрывается. Напряжение на емкости С1 принимает значение uC1 = –Un, а на емкости С2 равно нулю (иC1=0). После записи отключают напряжение на адресной шине.

Так как остаточный ток закрытого транзистора VT1 мал, то емкость С1 будет сохраняться на выходах ячейки (на стоках VT1 и VT2) длительное время За это время можно несколько раз считывать информацию ячейки (следует учитывать что при считывании приходится открывать транзистор VT4 и разряд С1 ускоряется). Для того чтобы поддерживать напряжение на емкости С1, несмотря на неизбежный ее разряд, осуществляют регенерацию: периодическую запись того же кода.

Динамические триггеры на МДП транзисторах экономичнее и компактнее триггеров на биполярных транзисторах, но уступают им по быстродействию.