Типовая структура БИС ОЗУ приведена на рис. 4.4.

Рисунок 4.4

Рисунок 4.5

Основным узлом является матрица ячеек памяти (МЯП), состоящая из n строк с т запоминающими ячейками (образующими разрядное слово) в каждой строке. Информационная емкость БИС памяти определяется по формуле N=nm бит.

Входы и выходы ячеек памяти подключаются к адресным АШ и разрядным РШ шинам. При записи и считывании осуществляется обращение (выборка) к одной или одновременно к нескольким ячейкам памяти. В первом случае используются двухкоординатные матрицы (рис. 4.5, а), во втором случае матрицы с пословной выборкой (рис. 4.5,6).

Дешифратор адресных сигналов (ДАС) при подаче соответствующих адресных сигналов осуществляет выбор требуемых ячеек памяти. С помощью РШ осуществляется связь МЯП с буферными усилителями записи (БУЗ) и считывания (БМС) информации. Схема управления записью (СУЗ) определяет режим работы БИС (запись, считывание, хранение информации). Схема выбора кристалла (СВК) разрешает выполнение операций записи-считывания данной микросхемы. Сигнал выборки кристалла обеспечивает выбор требуемой БИС памяти в ЗУ, состоящем из нескольких БИС.

Подача управляющего сигнала на вход СУЗ при наличии сигнала выборки кристалла на входе СВК осуществляет операцию записи. Сигнал на информационном входе БУЗ (1 или 0) определяет записываемую в ячейку памяти информацию. Выходной информационный сигнал снимается с БУС и имеет уровни, согласующиеся с серийными ЦИС.

Большие интегральные схемы ОЗУ стремятся на основе простейших элементов ТТЛ, ТТЛШ, МДП, КМДП, И2Л, ЭСЛ, модифицированных с учетом специфики конкретных изделий. В динамических ячейках памяти чаще всего используются накопительные емкости, а в качестве ключевых элементов — МДП транзисторы.

Выбор элементной базы определяется требованиями к информационной емкости и быстродействию БИС памяти. Наибольшей емкости достигают при использовании логических элементов, занимающих малую площадь на кристалле: и2л, МДП, динамических ЗЯ. Высоким быстродействием обладают БИС с логическими элементами, имеющими малые перепады логических уровней (ЭСЛ, И2Л), а также логические элементы ТТЛШ.

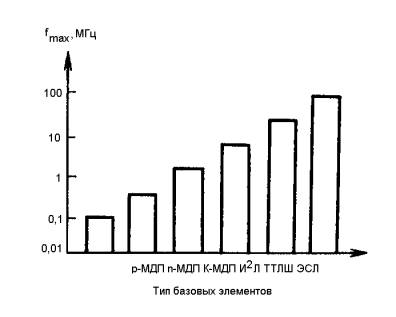

Частотные области применения БИС, использующих различные базовые технические решения, иллюстрирует рис. 4.6.

Рисунок 4.6

Благодаря развитию технологии и схемотехники быстродействие элементов непрерывно возрастает, поэтому границы раздела указанных областей с течением времени сдвигаются в область больших рабочих частот.