2. Цифровая коммутация каналов

3. Синтез цифрового модуля пространственной коммутации каналов

3.1. Функциональное описание коммутационного модуля

3.2. Метод синтеза регулярной структуры МПК с декомпозицией по выходам

3.3. Метод синтеза регулярной структуры МПК с декомпозицией по входам

3.3.1. Однокаскадная декомпозиция МПК

4. Синтез цифрового модуля временной коммутации каналов

4.1. Особенности временной коммутации каналов

4.3. Этапы структурного синтеза МВК

4.3.1. Определение необходимого объема памяти

4.3.3. Обеспечение временных параметров и быстродействия МВК

5. Синтез цифрового модуля пространственно-временной коммутации каналов

5.1. Структурирование процесса цифровой коммутации каналов

5.2. Методы структурного синтеза МПВК

5.3. Коммутационный модуль системы ЭАТС-200

1. Введение

Цифровые системы, используемые для коммутации речевой информация в режиме коммутации каналов, как правило, реализуют распределение информации путем преобразования координат сигналов и каналов, включаемых на входящую и походящую стороны соответственно. В настоящее время базовыми координатами, по которым разделяются цифровые каналы, являются время и пространство. Это связано с тем, что груп-дообразование каналов осуществляется на основе временного разделения, а в качестве метода кодирования используется импульоно-кодовая или дельта-модуляция. Учитывая, что временные каналы организуются в пространственно-разнесенных трактах, цифровая коммутация принципиально должна реализовывать два типа преобразований: изменение временной координаты канала (соответственно сигнала) и пространственной координаты канала (соответственно сигнала). Реализация каждого тина преобразований осуществляется в отдельном функционально-ориен-тированном модуле: цифровой коммутации каналов в пространстве, цифровой коммутации каналов во времени, гибридной коммутации цифровых каналов. Поэтому синтез всего цифрового коммутационного поля осуществляется путем синтеза соответствующих коммутационных модулей.

Задача синтеза каждого функционально-ориентированного цифрового коммутационного модуля нетривиальна и представляет собой по существу задачу проектирования многовходового и многовыходного дискретного устройства. В свою очередь задача синтеза цифрового коммутационного поля на базе коммутационных модулей относится к классическим задачам оптимизации структурно-сложных систем коммутации.

2. Цифровая коммутация каналов

В цифровой системе коммутации каждый сигнал XiI передается по ифровому каналу ki , принадлежащему определенному тракту R , т.е.

Xi ® ki , ki Î R , i =![]() . (1)

. (1)

Число каналов n в тракте определяется мощностью используемой системы передачи. В общем случае мощность входящих и исходящих цифровых трактов nпер не равна мощности внутристанционных цифровых трактов системы коммутации nкомм , причем возможны различные соотношения:

nпер < nком , nпр > nком , nnep = nком , (2)

|

которые определяются рядом факторов, в том числе обеспечением необходимых коммутационных возможностей системы.

Координаты каждого цифрового канала ki![]() как объекта коммутации определяются двумя координатами:

как объекта коммутации определяются двумя координатами:

- временной, определяемой номером временного интервала ti , отводимого каналу ki - в общем, цикле передачи системы Т;

- пространственной , определяемой номером Si цифрового тракта, которому принадлежит данный канал.

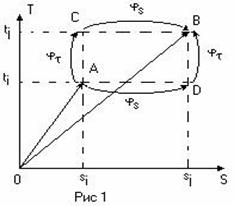

Таким образом, имеем векторное представление канала: ki - { Si,, ti } в двухкоординаторном пространстве S и Т (рис. I). Коммутация цифровых каналов - это процесс образования соединительного тракта в простейшем случае двух цифровых каналов:

ki(Si,, ti) « kj(Sj,, tj) (3)

Поскольку координаты S и Т, определяющие цифровые каналы, - ортогональны, то, следовательно, процесс коммутации Æ разбивается на 2 класса процессов:

js - преобразование пространственной координаты канала, т.е. пространственная коммутация;

jr - преобразование временной координаты канала, т.е. временная коммутация.

Последовательность процессов преобразования каждой координаты, а также число этапов преобразования каждого вида может быть различной, но каждой из них соответствует определенный класс структур коммутационных полей. В табл. I приведены некоторые из них.

Таблица I

| Последовательность | Структура коммутационного поля |

|

L1={js, jt } L1={jt, js } L1={jt ,js, jt } L1={js, jt , js, jt , js } |

пространство - время ( S , Т ) время - пространство ( Т, S ) время – пространство - время ( Т, S , Т ) пространство - время - пространство - - время - пространство ( S , Т , S , Т , S ) |

3. Синтез цифрового модуля пространственной коммутации каналов

3.1. Функциональное описание коммутационного модуля

Пусть имеем два канала ki{ Si,, ti }и kj{ Sj,, tj }. Пространственная коммутация этих каналов:

ki{ Si,, ti } ® kj{ Sj,, tj } (4)

в силу ортогональности S и Т имеет смысл, если ti = tj . Таким образом, пространственная коммутация цифровых каналов - это коммутация одноименных каналов различных трактов. Другими словами, пространственная коммутация цифровых каналов ki , kiÎR(Si) , и kj , kjÎR(Sj) сводится к коммутации цифровых трактов:

R(Si) ® R (Sj) (5)

в интервале ti .

Следует отметить, что коммутация цифровых трактов может осуществляться в различных интервалах ti (i = ![]() , где С - мощность тракта), что будет cоответствовать пространственной коммутации цифровых каналов ki тракта R(Si) с одноименными по временным интервалам каналами kj тракта R(Sj).

, где С - мощность тракта), что будет cоответствовать пространственной коммутации цифровых каналов ki тракта R(Si) с одноименными по временным интервалам каналами kj тракта R(Sj).

Построим функциональное описание процесса коммутации. Пусть имеем N входящих и М исходящих цифровых трактов, мощность каждого из которых равна С каналам. Поставим в соответствие каждому тракту логическую переменную: входящему – хi , исходящему – zj. Введем обобщенную переменную управления аij , определяющую обобщенный адрес коммутируемых трактов. Тогда, если считать, что результатом пространственной коммутации является прохождение сигнала по соединительному тракту от входящего к исходящему каналу, можно zj рассматривать как функцию пространственной коммутации и представить ее в виде булева уравнения:

zj = xi aij (6)

j

Если для рассматриваемого коммутационного модуля на M входящих и N походящих трактов выполняется условие полнодоступности, т.е. модуль может осуществлять коммутацию одноименных каналов любого входящего о любым исходящим трактом, то его функционально можно описать системой булевых функций:

GG: {zi = xi aij , i = ![]() , j =

, j = ![]() } (7)

} (7)

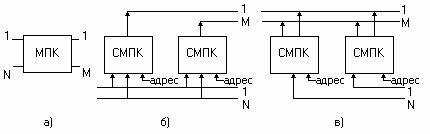

На основе системы (7) могут быть синтезированы различные структуры коммутационного модуля (рис. 2,а), однако наибольшее распространение получили регулярные структуры, образуемые при декомпозиции по выходам (рис. 2,6)

|

и декомпозиции по входам - (рис. 2,в), На рис. 2 приняты следующие обозначения: МПК-модуль пространственной коммутации, СМПК - субмодуль пространственной коммутации. Рассмотрим синтез этих структур.

3.2. Метод синтеза регулярной структуры МПК с декомпозицией по выходам

3.2.1. Одноканальная декомпозиция МПК

В этом случае множество булевых функций с разбивается на подмножества Gj![]() , j =

, j = ![]()

![]() , так что в подмножество Gj входят только те функции Z j , которые помечены одноименным индексом J , т.е.

, так что в подмножество Gj входят только те функции Z j , которые помечены одноименным индексом J , т.е.

Gj : Z j =Xj ai j , j = ![]() , (8)

, (8)

При этом поскольку коммутационный модуль обладает свойством полнодоступности , то, следовательно, подмножество Gj определяет компоненты обобщенной функции, соответствующей исходящему тракту:

Это справедливо для любого тракта, следовательно, коммутационный модуль можно описать системой H:

, j =

, j = ![]()

![]()

При декомпозиции по выходам переменная ![]() выступает в каждом СМПК в виде адреса входа (входящего тракта). Однако фактически при синтезе ШЛК этот адрес должен быть представлен совокупностью адресных переменных, значения которых определяются в результате кодарования. Обозначим через аαk переменные кодирования, где k=

выступает в каждом СМПК в виде адреса входа (входящего тракта). Однако фактически при синтезе ШЛК этот адрес должен быть представлен совокупностью адресных переменных, значения которых определяются в результате кодарования. Обозначим через аαk переменные кодирования, где k=![]() , α ª {0,1},

, α ª {0,1}, ![]() ,

, ![]() , тогда (10) можно переписать в виде

, тогда (10) можно переписать в виде

, j =

, j = ![]()

![]()

Следует иметь в виду, что при кодировании адреса ![]() возможны различные подходы: общее кодирование по всему множеству M x N либо раздельное. В настоящее время получило распространение раздельное Кодирование с ограничением, что обусловлено технологическими особенностями реализации управления коммутационным модулем. Поэтому для этого случая джина адреса U определяется как:

возможны различные подходы: общее кодирование по всему множеству M x N либо раздельное. В настоящее время получило распространение раздельное Кодирование с ограничением, что обусловлено технологическими особенностями реализации управления коммутационным модулем. Поэтому для этого случая джина адреса U определяется как:

![]()

Реализация МПК при декомпозиции по выходам наиболее эффективна при использовании мультиплексоров - избирательных схем типа N*1, осуществляющих коммутацию различных входных сигналов на один выход в соответствии с поступающим адресом. Мультиплексор в общем случае реализует функцию вида

где Z - выходная переменная, соответствующая выходу мультиплексора;

xi - входная переменная (вход мультиплексора);

fi (a) - функция адреса i -го входа.

Функция fi(a) представляет собой конъюнкцию адресных переменных аi,…,аk, дополняеляую иногда инверсией переменной S, соответствующей сигналу стробирования:

fi(a) = ![]() a1α1 … akαk

a1α1 … akαk![]() , αjÎ{0,1}, j=

, αjÎ{0,1}, j=![]() (14)

(14)

Сопоставляя (13) и (II), видим их полную функциональную идентичность. Таким образом, универсальный элемент мультиплексор можно использовать для реализации МПК.

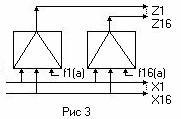

На рис. 3 приведена реализация МПК 16x16 на мультиплексорах К155КП1. Как видим, каждый мультиплексор реализует функцию

где

fi(a) =![]()

|

Полученная структура МПК называется однокаскадной, поскольку каждая функция реализуется одним мультиплексором. Такая структура получается в v том случае, когда число входящих трактов МПК N не превышает числа входов мультиплексора. Многокаскадная декомпозиция МПК

Если это условие не выполняется, то осуществляется многокаскадная декомпозиция МПК. Вернемся к функции МПК:

Пусть имеется в распоряжении один тип мультиплексора с параметрами (n ,r ), где n - число его информационных, г- адресных входов. Тогда при определении числа необходимых каскадов следует исходить из соотношения nq-1≤N≤nq или преминительно к адресу (q-1)r≤k≤qr.

Конъюнкция адресных переменных в (15) примет в этом случае вид

Результирующая функция выхода zj образуется как композиция функций отдельных каскадов: zj=F1* F2*… Fq, где

Таким образом, результирующая функция выхода для одного субмодуля МПК примет вид

![]()

Если в распоряжении проектировщика оказывается набор различных мультиплексоров, то решается задача оптимизации числа каскадов и числа элементов для их покрытия. Эта задача относится к классической задаче минимизации булевых функций.

3.2.2. Примеры синтеза МПК

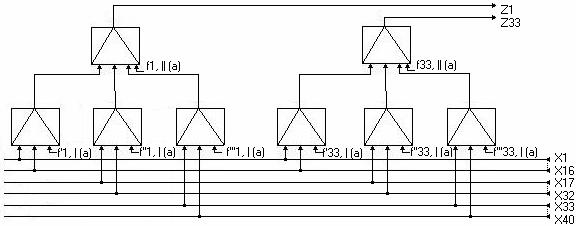

Рассмотрим пример синтеза МПК с параметрами N = 40, М = 40. При декомпозиции по выходам имеем функциональное описание:

{zj = x1a1j ![]() x2a2j

x2a2j ![]()

![]() ….

…. ![]() x40a40j j = 1,40 }

x40a40j j = 1,40 }

Определим длину адресной конъюнкции aij, имея в виду различное кодирование: u = ] log2 40 [ = 6

Пусть требуется реализовать этот МПК на мультиплексорах типа К155КП1 с параметрами n =16, г = 4. Сначала определим необходимое число каскадов q :

16q-1≤40≤16q → q = 2

Строим разбиение функций Fp . Дяя этого сначала определим p :

x = {x1,….,xp} = ]![]() [=]

[=]![]() [ = 3

[ = 3

Разбиваем множество входных переменных x = {x1,…,x40} на подмножества мощности не выше n = 16:

x1 = {x1,…,x16}

x2 = {x17,…,x32}

x3 = {x33,…,x40}

Теперь записываем функции Fp , р = {I, 2, 3}:

Строим композицию функций выхода одного субмодуля:

На основе полученной функция cтроим реализацию МПК, как показано на. рис. 4.

|

В табл.2 приведены некоторые типы мультиплексоров, которые могут быть использованы для построения МПК. Таблица 2

|

Тип мультеплексора |

Число коммутир. входов |

Число адресных входов |

|

К155КП1 |

16 |

4 |

|

К555КП12 К531КП2 КМ155КП2 |

4x2 |

2 |

|

К155КП5 К5551П15 КМ155КП5 |

8 |

3 |

|

К1551П7 K56IKП2 КМ155КП7 |

8 |

3 |

3.3. Метод синтеза регулярной структуры МПК с декомпозицией по входам

3.3.1. Однокаскадная декомпозиция МПК

В этом случае множество булевых функций G разбивается на подмножества

Bi , i =![]() , так, что в подмножество Вi входят только те функции zi , которые содержат входящую переменную xi

, так, что в подмножество Вi входят только те функции zi , которые содержат входящую переменную xi

Вi : {zj = xi aij , j = ![]() } (19)

} (19)

Ради удобства промаркируем функции этого множества индексом i:

Вi : {![]()

![]() = xi aij } (20)

= xi aij } (20)

Теперь можно построить композицию каждой функции выхода МПК:

zi : {![]() *

* ![]() *….*=

*….*= ![]() , j =

, j = ![]() } (21)

} (21)

Таким образом каждое подмножество функций В1 определяет субмодуль с одним входящим трактом xi и всеми исходящими трактами zj , j = ![]() . Композиция (21) обеспечивает свойство полнодоступности модуля за счет объединения одноименных выходов разных субмоделей (см. рис. 2,в). Процедура синтеза при декомпозиции по входам аналогична рассмотренной выше. Здесь также используется раздельное кодирование и каждая функция подмножества

. Композиция (21) обеспечивает свойство полнодоступности модуля за счет объединения одноименных выходов разных субмоделей (см. рис. 2,в). Процедура синтеза при декомпозиции по входам аналогична рассмотренной выше. Здесь также используется раздельное кодирование и каждая функция подмножества![]() Вi раскрывается в виде:

Вi раскрывается в виде:

(22)

(22)

где

![]()

![]() (23)

(23)

Реализация МПК при декомпозиции по входам наиболее эффективна на

демультиплексорах. Это избирательная схема 1![]() m с одним входом, сигналы c которого могут переключаться на один из m выходов в соответствии с поступающим адресом. Обозначим через хi - вход, z1,…,zm – выходы, fj(a)- адрес

m с одним входом, сигналы c которого могут переключаться на один из m выходов в соответствии с поступающим адресом. Обозначим через хi - вход, z1,…,zm – выходы, fj(a)- адрес

j-го выхода, тогда функционирование демультиплексора можно описать системами булевых функций

Pi , i = ![]()

Pi : {zj = xi fj (a)} , j = ![]() (24)

(24)

Сопоставляя (22) и (24), можно видеть, что выражения функционально идентичны. Следовательно, универсальный элемент демультиплексор можно использовать для синтеза МПК.

|

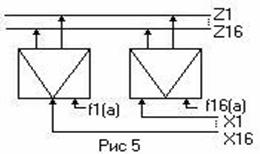

На рис. 5 приведена реализация МПК на демультиплексорах. Как видим, каждый демультиплексор реализует функции соответственно:

z1 = x1 f1(a), z 2= x2 f2(a)

z3 = x3 f3(a), z 4= x4 f4(a)

где

fi(a) = ![]()

Полученная структура называется однокаскадной, поскольку каждый субмодуль реализуется одним домультиплексором.

3.3.2. Многокаскадная декомпозиция МПК

Однако так же, как в случае декомпозиции по выходам, возможны ситуации, когда число исходящих трактов модуля больше числа коммутируемых выходов демультиплексора. В этом случав осуществляется многокаскадная декомпозиция МПК. Подход к ее осуществлению аналогичен выщерассмотренному, т.е. сначала определяется необходимое число каскадов q , исходя из соотношения М и m :

q = ]![]() [

[

В соответствии о полученным числом каскадов определяется разбиение множества выходов по множеству демультиплексоров. Затем строится композиция выходных функций и соответственно выходов на каждом каскаде.

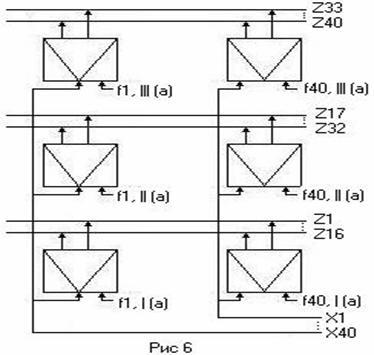

3.3.3. Примеры синтеза МПК

Рассмотрим пример синтеза MПK с параметрами N = 40, М = 46. При декомпозиции по выходам имеем функциональное описание МПК в виде:

Определяем длину адресной конъюнкции aij : v =]log246[=6

Пусть требуется реализовать этот МПК на демультиплексорах типа К155ИД3 с параметрами m = 16, r = 4. Сначала определяем число каскадов q :

q = ]![]() [=]

[=]![]() [=3

[=3

Затем cтроим разбиение множества выходов z = {z1, ... , z46} на подмножества мощностью не выше m = 16: Z1 = {z1 ,... , z16}, Z2 = {z17 ,... , z32}, Z3 = {z33 ,... , z46}.

Теперь расписываем функции по каскадам: Z1 - первый каскад, Z2 - второй каскад, Z3 - третий каскад.

Строим композицию функций одного субмодуля МПК:

На основе полученной композиции строим реализацию МПК, как показано на рис. 6.

В табл. 3 приведены некоторые типы демультиплексоров, которые можно использовать для синтеза МПК.

Таблица 3

|

Тип демультиплексора |

Число коммутир. выходов |

Число адрес, входов |

Строб. |

|

К155ИДЗ К155ИД4 |

16 2х4 |

4 2 |

есть есть |

|

Здесь мы рассмотрели проблему синтеза МПК с точки зрения реализации процесса коммутации, не касаясь проблем управления коммутацией, т.е. адресации и распределения. Это сложная проблема, которая требует отдельного рассмотрения.

4. Синтез цифрового модуля временной коммутации каналов

4.1. Особенности временной коммутации каналов

|

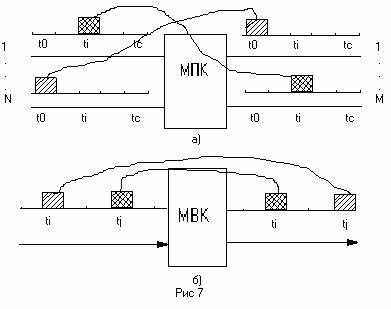

Коммутация цифровых каналов во времени состоит в обеспечении возможности передачи информации, поступающей в одном временном интервале ti , в течение другого временного интервала tj. Поскольку моменты поступления и выдачи информации разнесены во времени, то процесс коммутации обязательно включает хранение информации в течение времени

Цифровые каналы организуются в четырехпроводных трактах передачи, поэтому следует иметь в виду, что при временной коммутации устанавливается полное дуплексное соединение, которое обеспечивает информационный обмен в обоих направлениях передачи.

4.2. Режимы работы МВК

Функция хранения информации в МВК современных цифровых систем коммутации реализуется с помощью запоминающего устройства с произвольным (прямым) доступом к хранимым данным. Это ЗУ и соответственно МВК может работать в двух режимах: первый - последовательной (циклической) записи и произвольной выборки (ациклического чтения); второй - произвольной записи и последовательной выборки. Первый режим обозначают(→↓;↕→) , второй - (→↕;↓→) В первом случае входящий цифровой тракт заводится на информационные шины (ШИ) МВК, и информация, поступающая по цифровым каналам, последовательно записывается в ячейки ЗУ, начиная с первой; при этом обычно номер ячейки соответствует номеру временного интервала в цикле системы передачи, занимаемому цифровым каналом. Адреса записиАс поступают на шину адреса ША обычно от счетчика каналов.

|

При произвольной выборке реализуется обращение к определенной ячейке ЗУ, адрес Ау которой вырабатывает управляющее устройство. Процесс временной коммутации канала ki с каналом kj протекает следующим образом. В режиме записи на ША от счетчика адресов в течение интервала ti поступает адрес 1-й ячейки, в которую записывается информация, передаваемая в канале ki , а в течение tj - адрес j-ой, в которую записывается информация, передаваемая в канале kj. B режиме чтения на ША из УУ в течение интервала ti поступает адрес j-й ячейки, и записанная в ней информация списывается в канал ki . Аналогично в течение интервала tj на ША из УУ поступает адрес с i-и ячейки, и записанная в ней информация списывается в канал kj. Таким образом, осуществляется взаимный обмен информацией каналов ki и kj , т.е. устанавливается полное дуплексное соединению (рис. 8).

В режме (→↕;↓→) адреса записи вырабатываются управляющим устройством, и информация, поступающая в следующих друг за другом каналах входящего тракта, записывается в общем случае не в последовательно расположенные ячейки , а в те , которые соответствуют коммутируемым каналам исходящего тракта. При чтений ЗУ адреса обращения вырабатываются счетчикому и содержимое всех ячеек памяти, начиная с первой, последовательно считывается в соответствующие по номеру каналы исходящего тракта. Процесс коммутации канала ki и kj протекает следующим образом. В режиме записи в течение интервала ti на ША из УУ поступает адрес j-й ячейки, в которую записывается информация канала ki. Соответственно в течение интервала tj на ША поступает адрес i-й ячейки, в которую записывается информация канала kj. При чтении информация j-й ячейки будет считана в интервале tj, a i-й - в интервале ti . Таким образом, устанавливается полное дуплексное соединение двух цифровых каналов.

Выбор режима работы ВК определяется на этапе системного проектирования .

4.3. Этапы структурного синтеза МВК

Реализация процесса временной коммутации цифровых каналов сводится к определению необходимого объема памяти, выбору типа ОЗУ из номенклатуры выпускаемых промышленностью, организации памяти, учету требований к быстродействию модуля, выбору способа ввода/вывода информации в память МВК.

4.3.1. Определение необходимого объема памяти

Определение необходимого объема памяти производят, исходя из числа цифровых каналов, организуемых в тракте; длины кодового слова, передаваемого в одном канале, а также режима работы МВК. Если число каналов входящего и исходящего трактов С1 и С2 соответственно, то необходимый объем ЗУ (в битах)

в режиме (→↓;↕→) : V*= C1 1,

в режиме (→↕;↓→) : V**= С2 1.

Следует заметить, что в общем случае объем памяти можно определять, исходя из максимальной мощности тракта передачи, имея в виду возможность реализации любого режима. С другой стороны, это может оказаться целесообразным, если учесть, что в таком случае мы получаем возможность построения различных альтернативных решений при синтезе структуры коммутационного поля: введение концентрации или расширения, построение полнодоступной или неполнодоступной схемы и т.д.

Для иллюстрации приведем пример. Пусть требуется построить МВК без сжатия и расширения, по полнодоступной схеме, который должен выполнять временную коммутацию каналов системы передачи ИКМ-120. Известно, что длина слова в канале ИКМ-120 l=8, мощность системы С =120 информационных каналов, следовательно, необходимый объем памяти составит V=120 х 8=960, бит.

4.3.2. Организация памяти

На этом этапе решается задача построения ОЗУ БВК заданного объема на основе стандартных полупроводниковых ЗУ, выпускаемых промышленностью. В цифровых системах коммутации находят применение полупроводниковые ЗУ с произвольной выборкой различной емкости, начиная с ЗУ на элементах средней степени интеграции типа K-I55 РУ-2 16x4 до ЗУ на БИС-одно- и многокристальных. В системах используются как статические, так и динамические ЗУ. В статических ЗУ в качестве элементов памяти используются триггерные схемы различных типов, объединяемые в некоторую регулярную структуру, управляемую сигналом записи/считывания (3/С) и сигналом выбора кристалла (ВК). Чтение и запись информации происходит по адресу, поступающему в ЗУ по адресным шинам. Расшифровка адреса выполняется в дешифраторе, который обычно реализуется в том же кристалле, что и ЗУ. В современных динамических ЗУ в качестве элемента памяти используется емкость затвор-канал МОП-транзистора, которая при записи информации заряжается. Однако время хранения заряда невелико (порядка 10-3 ), поэтому требуется периодический ее подзаряд, т.е. регенерация записанной информации. Этот процесс выполняется под действием внешних тактовых импульсов, причем схемы регенерации могут быть как вынесенными, так и совмещенными на одном кристалле с матрицей памяти. При пропадании тактовых импульсов информация в ЗУ разрушается. Как известно, реализация элемента памяти в статическом ЗУ обходится вдвое дороже по количеству транзисторов, чем динамические ЗУ, которые к тому же обладают более высоким быстродействием и меньшей потребляемой мощностью (всего несколько мкВт/бит). Однако необходимость реализации схем регенерации в динамических ОЗУ обычно ограничивает эффективность использования их только для ЗУ большой емкости. Поэтому для ЗУ малой и средней емкости обычно используются статические ЗУ.Однако оба типа ЗУ обладают общим существенным недостатком - разрушением информации при отключении источников питания.

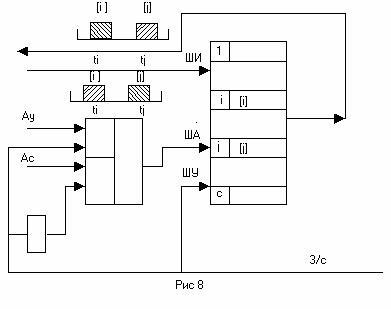

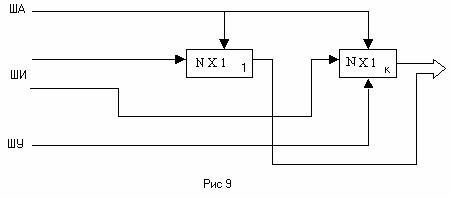

Каждое ЗУ имеет адресные шины ША, по которым поступает адрес ячейки памяти; входные информационные шины ШИ, по которым поступает информация для записи в память; выходные ШИ, по которым информация выдается из памяти, и сигналы управления: сигнал запись/считиваяие (3/С), определяющий режим работы ЗУ; сигнал выбора кристалла (ВК), используемый при организации нескольких блоков ЗУ, связанных общей выходной шиной; и предназначенный для отключения в случае необходимости данного субблока ЗУ от общей шины. В динамическом ЗУ, кроме того, имеется управляющий сигнал синхронизации "СИНХ", который используется, во-первых, для заряда выходных емкостей перед чтением информации и, во-вторых, для синхронизации сигнала ВК.

|

В общем случае ЗУ может иметь несколько управляющих сигналов ВК, но при наличии одного ВК обращение к ЗУ происходит, если ВК = 1, и заблокировано, если ВК = 0. Сигнал 3/С - дуальный: если он присутствует, т.е. 3/С = 0, то ЗУ находится в режиме записи; если нет, т.е. 3/С =1, то ЗУ находится в режиме считывания (хранения). В обоих режимах (записи и считывания) адресные сигналы подаются до поступления управляющих сигналов ВК и 3/С. В табл. 4 приведены характеристики некоторых типов ОЗУ. Как видно, на одном БИС ЗУ реализуется некоторое конечное число однобитовых слов (от 0,25 к до 16 к), т.е. память имеет структуру Nxl) бит. Поэтому для образования требуемой длины слова хранения необходимо выбрать число БИС, равное числу разрядов слова. На рис. 9 приведен пример организации памяти для случая хранения k -разрядного слова и общей емкости (N![]() k) бит. Совокупность k одноразрядных выходных шин данных всех БИС ЗУ образует k-разрядную шину данных системы памяти. Для реализации одновременного обращения ко всем k БИС ОЗУ и ША. и ШУ всех БИС запараллеливаются.

k) бит. Совокупность k одноразрядных выходных шин данных всех БИС ЗУ образует k-разрядную шину данных системы памяти. Для реализации одновременного обращения ко всем k БИС ОЗУ и ША. и ШУ всех БИС запараллеливаются.

При построении БВК цифровых систем коммутации может возникнуть необходимость в построении ЗУ с числом слов, большим N. В этом случае используется страничная организация памяти. Каждый субблок системы N![]() K образует "страницу" памяти, к которой адресуются по шине ШA, по которой поступает адрес страницы-субблока. Выборка требуемого слова памяти производится по адресу, поступающему на шины адреса ША каждого субблока. Для того, чтобы отключить от общей шины ШИ невыбранные субблоки, используется сигнал выбор кристалла (ВК), который управляет трехстабильной схемой ввода/вывода на каждом кристалле ЗУ, переводя ее в третье состояние, называемое состоянием разомкнутой цепи или высокого сопротивления.

K образует "страницу" памяти, к которой адресуются по шине ШA, по которой поступает адрес страницы-субблока. Выборка требуемого слова памяти производится по адресу, поступающему на шины адреса ША каждого субблока. Для того, чтобы отключить от общей шины ШИ невыбранные субблоки, используется сигнал выбор кристалла (ВК), который управляет трехстабильной схемой ввода/вывода на каждом кристалле ЗУ, переводя ее в третье состояние, называемое состоянием разомкнутой цепи или высокого сопротивления.

Таблица 4

|

Тип микро-схемы п/п 0ЗУ |

Технология |

Информа ционная емкость, слов х разрядов |

Длина адрес-ного слова, бит |

Время обра-щения,нс |

Напряже-ние пи-тания, В |

Потребляе-мая мощ-ность, мВт |

|

КI55РУ5 |

ТТЛ |

256 |

8 |

60 |

5 |

700 |

|

КI88РУ2А |

ТТЛ |

256 |

8 |

500 |

5 |

стат:250 дин:500 |

|

КI76РУ2 |

К-МОП |

256 |

8 |

550 |

||

|

К500РУ410 |

ЭСЛ |

256 |

8 |

25 |

-5, 2 |

750 |

|

К500РУ415 |

ЭСЛ |

1024 |

10 |

30 |

-5, 2 |

730 |

|

КР565РУ2А |

п-МОП |

1024 |

10 |

400 |

12;5;-5 |

300 |

|

КI55РУ1А |

ТТЛ |

2048 |

11 |

400 |

5 |

|

|

КР565РУ1А |

п-МОП |

4096 |

12 |

200 |

12;5;-5 |

3;0,25;0,125 |

|

КI55РУ1Б |

ТТЛ |

4096 |

12 |

400 |

5 |

|

|

КР541РУ31 |

ЭСЛ |

8192 |

13 |

150 |

5 |

550 |

|

КР541РУ3 |

ЭСЛ |

16384 |

14 |

150 |

5 |

550 |

4.3.3. Обеспечение временных параметров и быстродействия МВК

На этом этапе решается задача выбора необходимых средств и методов для обеспечения динамических характеристик МВК. В настоящее время существует ряд подходов к построению МВК, которые обусловлены различными возможностями разработчиков по использованию элементной базы. Дело в том, что одним из основных требований к ЗУ, на основе которых строится МВК, является время цикла (обращения) памяти, определяющее частоту работы ЗУ. Реализация процесса временной коммутации в МБК требует двух обращений к памяти в течение одного временного интервала для каждого входящего и исходящего каналов. Следовательно, если цикл системы передачи равен Тц, а число организованных в нем каналов С, то время обращения у ЗУ (длительность цикла памяти) τ≤Тц/2С. Это позволяет осуществить выбор требуемого БИС ЗУ для БВК, исходя из требований коммутации. С другой стороны, если известен цикл системы передачи Тц и задан тип ЗУ, то можно определить максимальное число каналов, которое может обслужить БВК при заданном быстродействии ЗУ – τ: С≤Тц/2 τ.

Пусть, например, БВК должен осуществить коммутацию цифровых каналов, образованных на базе ИКМ, с временем цикла Тц = 125 мкс и для его построения используется ЗУ с временем обращения τ = 560 нс, тогда определяем

С≤![]() =

= ![]() = 125 каналов.

= 125 каналов.

Таким образом, БВК может обслужить 125 дуплексных каналов и установить 62 дуплексных соединения.

С другой стороны, если БВК должен обслуживать 480 цифровых каналов с

Тц = 125 мкс, то он может быть построен на ЗУ, у которого

τ ≤![]() =

= ![]() = 0,130 , мкс.

= 0,130 , мкс.

Например, для построения БВК можно выбрать БИС К500РУ415 1024x1 с временем цикла 30 нс или К155РУ5 256x1 с временем цикла 60 нс.

Как вытекает из рассмотренных выше примеров, требования к быстродействию БВК являются достаточно жесткими и для их удовлетворения необходимо либо выбирать соответствующую элементную базу с высокими показателями по быстродействию, либо применять структурные методы.

Одним из таких методов является метод двойной памяти, суть которого состоит в том, что для обеспечения непрерывного действия МВК его память удваивают, вводя два идентичных блока ЗУ; моменты записи и считывания в каждый блок разносят во времени так, что во время записи информации в один блок из другого ведут считывание.

При решении задачи структурного синтеза МВК в реальных цифровых системах коммутации чаще всего используют именно этот метод двойной памяти, что позволяет существенно снизить требования по быстродействию к элементной базе. Если учесть, что, например, используемые на телефонных сетях системы

МТ 20/25 и АТСЭ-200 были разработаны в семидесятые годы, то, естественно, обеспечение требуемых временных параметров системы в части скорости коммутации достигалось за счет определенных аппаратных затрат.

На рис. 10 приведена функциональная схема МВК, построенная по методу двойной памяти. Она включает коммутаторы шин адреса КША1 и KША2, каждый из которых обеспечивает коммутацию адресных шин ОЗУ МВК с выходами Aс счетчика адресов при записи в ОЗУ и с выходами Ау периферийного управляющего устройотва при считывании из ОЗУ.

Сигнал управления 3/С определяет работу пары идентичных ОЗУ. При его поступлении в ОЗУ1 начинается запись в него информации, передаваемой в цифровых каналах тракта передачи, заведенного на информационные шины (ШИ) и ОЗУ1 и ОЗУ2. Одновременно инверсия сигнала 3/С управляет считыванием из ОЗУ2 информации, которая была занесена в него в предыдущем цикле передачи. При изменении значения сигнала 3/С происходит соответствующее изменение режима работы ОЗУ1 и ОЗУ2: ОЗУ2 начинает накапливать информацию, поступающую в цифровых каналах входящего тракта передачи, а ОЗУ1 - считывать информацию в исходящий тракт. Очевидно, что для исключения потери информации при использовании метода двойной памяти скорость переключения сигнала 3/С должна быть не меньше частоты следования циклов, т.е.

Как видим, помимо снижения требования к быстродействию элементов, использование метода двойной памяти позволяет: fЗ/С≥1/Тц.

обеспечить простоту реализации МБК;

довести скорость работы ОЗУ МВК до скорости, равной скорости цифрового потока системы передачи.

Эти возможности метода и привлекли разработчиков систем коммутации к его использованию. Однако метод двойной памяти имеет ряд недостатков. Первый состоит в том, что при реализации МВК по такой схеме необходимо особое внимание уделять синхронизации работы ОЗУ, поскольку МВК поставлен в жесткие временные рамки.

Второй недостаток связан с тем, что коммутация в таком МВК сопровождается дополнительной задержкой информации: τзад ≤ 2ТЦ.

И, наконец, третий недостаток связан с аппаратными затратами: удвоением минимально необходимого объема памяти.

Тем не менее метод двойной памяти получил распространение в цифровых системах коммутации.

4.3.4. Выбор способа ввода/вывода информации в память МВК

Информация, передаваемая по цифровым каналам, поступает на МВК в виде цифрового потока, при этом запись ее в память в общем случае можно осуществлять по мере поступления, если имеются соответствующие ресурсы о необходимым быстродействием. Однако, учитывая жесткие временные ограничения на работу МВК и возможности имеющейся элементной базы, чаще всего осуществляют переход из последовательной формы передачи информации в параллельную на входе МВК и обратное преобразование на выходе. Для реализации этого преобразования обычно используют сдвигающие регистры. Поскольку для накопления в регистре всей информации, поступающей в течение цикла в данном канале ki, затрачивается весь интервал времени ti, то, очевидно, считывание информации из регистра для последующей записи в ОЗУ МВК возможно только в следующий интервал времени tj. Таким образом, последовательно-параллельное преобразование влечет за собой потерю времени передачи, т.е. задержку информации. Для ее компенсации обычно используют пару сдвигающих регистров и организуют их работу так, что пока идет запись и накопление информации в один, из другого идет в это время считывание.

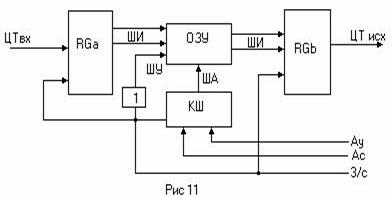

Переход к использованию в цифровых системах коммутации БИС памяти со структурой Nх1 привел к новым подходам к синтезу МВК, в том числе в части способа ввода-вывода информации в память. На рис. 11 приведена функциональная схема МВК на ОЗУ с однобитовыми ячейками, запись информации в которое осуществляется последовательно бит за битом по мере поступления цифрового потока передачи на вход МВК. При таком подходе необходимость в послетовательно-параллельном преобразовании сигналов, передаваемых по цифровым каналам, отпадает. Управляющий сигпал 3/С (по существу синхронизироваяная тактовая последовательность) открывает процесс записи информации из входящего цифрового информациовного тракта во входной регистр RGA. Под действием сигнала З/С происходит запись информационного бита кодовой комбинации i-го канала входящего тракта в RGA. Одновременно под действием этого же сигнала 3/С при условии поступления адресного сигнала Aу из периферийного управляющего устройства происходит считывание информации из ОЗУ и запись информационного бита кодовой комбинации j-го канала в RGВ. При изменении значения сигнала 3/С и при условии поступления адресного сигнала Ао из счетчика адресов в ОЗУ под действием инверсированного сигнала З/С происходит перезапись того же бита из RGA в ячейку памяти ОЗУ. Затем вновь при

|

изменении значения сигнала З/С происходит запись следующего бита кодовой комбинации i-го в RGA и перезапись из ОЗУ в RGA следующего бита j -го канала. Процесс коммутации продолжается аналогично для всех каналов тракта передачи. Очевидно, при таком построении МВК и последовательном способе ввода информации частота переключения сигнала З/С должна быть по крайней мере в 2 раза больше скорости следования информационных бит тракте передачи: fЗ/С≥2/τбит. Для примера, если цифровой тракт образован на базе системы передачи ИКМ-120 с общим числом каналов C1 = 128, то имеем (в упрощенном варианте):

Тц=125 мкс,

tкан= ![]() =

=![]() = 0,98 = 980 нс

= 0,98 = 980 нс

τбит = ![]() =

=![]() =125 нс

=125 нс

![]() =

=![]() = 16,39 МГц

= 16,39 МГц

fЗ/С≥16,39 МГц

Таким образом, последовательный способ ввода информации при использовании ОЗУ с однобитовыми ячейками позволяет обеспечить минимальную задержку информации и требует минимального объема памяти. Однако реализация МВК по такой схеме, как можно ожидать, окажется достаточно сложной, при этом временной режим МВК становится более жестким, поскольку требуемая скорость работы ОЗУ должна превышать скорость цифрового потока по крайней мере в 2 раза. Это существенно увеличивает требования по быстродействию к используемой элементной базе.

5. Синтез цифрового модуля пространственно-временной коммутации каналов

5.1. Структурирование процесса цифровой коммутации каналов

Рассмотренные ранее процессы коммутации предполагали для своей реализации разделение блока пространственной и временной коммутации цифровых каналов. Однако теоретически была доказана эффективность комбинированной коммутации и создания универсальных модулей пространственно-временной коммутации МПВК. Реализация этого стала возможной лишь с созданием более современной технологии, которая позволяет строить не только универсальные, но и специализированные БИС, в том числе и с настраиваемойoструктурой. В настоящее время существуют различные способы структурирования процесса пространст-венно-временной коммутации, каждый из которых определяет метод синтеза модуля МПКВ.

Рассмотрим процесс коммутации на примере. Пусть требуется скоммутировать два канала ki и kj :

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj }

, tj }

где i = ![]() ; j =

; j = ![]() ; S1,SM ª S; ti , tj ª T

; S1,SM ª S; ti , tj ª T

Распишем., процесс с коммутации для каждого варианта суруктуры.

1. Æ =φSφτ ;

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj },

, tj },

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj };

, tj };

2. Æ =φτ φS,

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj },

, tj },

kj{ ![]() , tj } ® kj{

, tj } ® kj{ ![]() , tj };

, tj };

3. Комбинированная коммутация осуществляется путем двойного эквивалентного преобразования (фиксированного): пространственной координаты

Si ª S в дополнительную временную tgiª Tg - преобразование ![]() и обратное преобразование

и обратное преобразование ![]() . При этом выполняется однозначное соответствие:

. При этом выполняется однозначное соответствие:

Si↔tgi , S↔Tg .

Тогда процесс коммутации протекает так:

Æ =![]() φτ

φτ ![]() ;

;

ki{ ![]() , ti } ® kn{

, ti } ® kn{ ![]() , ti};

, ti};

kn{ ![]() , ti } ® km{

, ti } ® km{ ![]() , tj };

, tj };

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj }.

, tj }.

Легко видеть, что фиксированное преобразование ![]() описывает процесс мультиплексирования (каналообразования в соединительном сверхтракте), а преобразование

описывает процесс мультиплексирования (каналообразования в соединительном сверхтракте), а преобразование ![]() - процесс демультиплексирования.

- процесс демультиплексирования.

5.2. Методы структурного синтеза МПВК

Методы структурного синтеза модуля пространственно-временной коммутации цифровых каналов определяются во многом возможностями технологии. При построении МПВК на базе универсальных ИС средней и большой степени интеграции все преобразования (во времени, в пространстве, параллельно-последовательное и обратное, мультиплексирование и демультиплексирование) выполняются в отдельных функциональных узлах, объединяемых в схему в соответствии с реализуемым процессом.

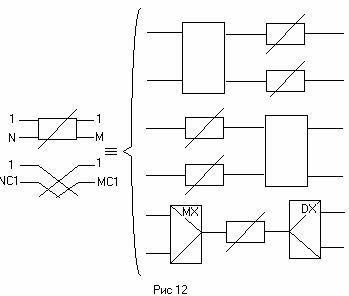

|

На pиc. 12 приведены три базовые структуры МПВК, которые положены в основу коммутационных модулей цифровых систем коммутации. Первая структура реализует последовательность (S-T), вторая (T-S), третья {(Т/ S) Т(Т/S)}. Каждая из них с той или иной модификацией нашла применение в конкретных системах. Рассмотрим некоторые из них.

5.3. Коммутационный модуль системы ЭАТС-200

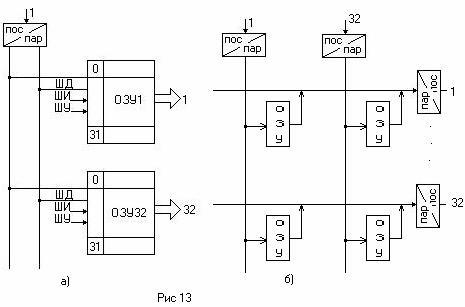

Модуль реализует Æ =φτ φS на множестве цифровых каналов N=1024, образованных в n = 32 цифровых трактов ИКМ по 32 канала в каждом. Учитывая уровень технологии на этапе разработки системы ЭАТС-200, был принят параллельный способ ввода информации в ОЗУ, поэтому на входе и выходе модуля устанавливаются устройства последовательно-параллельного и параллельно-последовательного преобразования соответственно. Их введение, как мы уже отмечали при синтезе МВК, позволяет, с одной стороны, снизить требования к быст-родействию элементной базы, а с другой стороны, обеспечить приемлемую скорость коммутационных процессов при временном преобразовании.

Рассмотрим реализацию коммутационных процессов в модуле: временное преобразование φτ осуществляется в памяти - ОЗУ, пространственное φS - физическим разделением выходов в пространстве. Рис. 13,а иллюстрирует принцип построения компоненты модуля для одного входящего тракта. Как видим, каждый исходящий тракт связан с одним ОЗУ, поэтому для 32 трактов введено 32 ОЗУ. В модуле выбран режим работы ОЗУ - (→↓;↕→). Поэтому технологически процесс cтроится так. В течение каждого цикла передачи Тц информация всех каналов тракта передачи записывается последовательно в одноименные ячейки всех 32 ОЗУ. Таким образом, частота обновления или подтверждения информации в памяти определяется циклом передачи и составляет для данного случая 8 кГц. Поэтому иногда информационный блок цикла называют 8-килогерцевым блоком. Управление коммутацией сводится к выбору соответствующего требованию ОЗУ - пространственная коммутация входящего тракта с исходящим, и выбору ячейки выбранного ОЗУ для считывания информации - временная коммутация цифровых каналов в скоммутированных трактах.

При построении МПВК в системе АТСЭ-200 используется метод двойной памяти, т.е. ОЗУ выполняется на двух идентичных параллельных схемах. Это позволяет использовать элементы памяти, в которых тактовая частота лежит в пределах 8 МГц. Если учесть период разработки системы и имеющиеся пределы допустимого быстродействия элементной базы того времени - тактовая частота до 10 МГц, то такое решение в построении МПВК становится вполне понятным. Модуль набирается из 32 компонент 1x32, как показано на рис. 13,б, путем объединения одноименных выходов. Для того, чтобы скоммутировать канал kiЦТ1 с каналом kjЦT32, необходимо установить полное дуплексное соединение, т.е.

kiЦТ1 → kjЦT32

kjЦT32 → kiЦТ1

Следовательно, пропускная способность коммутационного модуля составляет максимум 16 соединений.

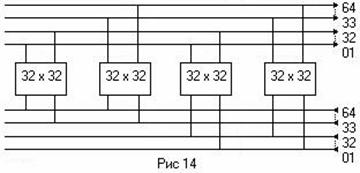

Модуль МПВК 32x32 является базовым модулем системы АТСЭ-200. На его основе строятся ступени искания системы емкостью 96x96; 128x128; 256x256 цифровых трактов. Построение осуществляется стандартным запараллеливанием входов и выходов МПВК, число которых выбирается в зависимости от требуемой емкости. Структуры получаются неэкономичными в силу квадратичной зависимости объёма оборудования от емкости системы. Например, если требуется построить коммутационный блок 64x64, т.е. увеличить емкость модуля вдвое, то для этого потребуется четыре модуля 32x32, т.е. четырехкратное увеличение оборудования (рис. 14).

|

5.4. Коммутационный модуль системы "Линия U Т"

Модуль реализует процесс коммутации Æ =![]() φτ

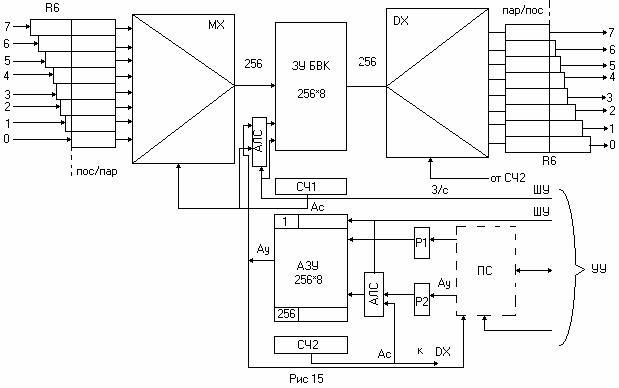

φτ ![]() для 256 цифровых каналов восьми цифровых трактов ИКМ, каждый на 32 канала. Таким образом, параметры МПВК: 8x8 трактов или 256x256 цифровых каналов. Рис. 15 иллюстрирует принцип построения МПВК и реализацию процесса коммутации.

для 256 цифровых каналов восьми цифровых трактов ИКМ, каждый на 32 канала. Таким образом, параметры МПВК: 8x8 трактов или 256x256 цифровых каналов. Рис. 15 иллюстрирует принцип построения МПВК и реализацию процесса коммутации.

Первый этап процесса коммутации ![]() -τ включает преобразование из последовательной формы в параллельную и последующее мультиплексирование. Он реализуется группой сдвигающих и буферных регистров RG, приданных каждому входящему цифровому тракту, и мультиплексором MX, управляемым счетчиком входящих трактов С41 . Число разрядов Si каждого регистра определяется длиной кодового слова (для ИКМ - 8 бит) и преобразованием

-τ включает преобразование из последовательной формы в параллельную и последующее мультиплексирование. Он реализуется группой сдвигающих и буферных регистров RG, приданных каждому входящему цифровому тракту, и мультиплексором MX, управляемым счетчиком входящих трактов С41 . Число разрядов Si каждого регистра определяется длиной кодового слова (для ИКМ - 8 бит) и преобразованием ![]() -τ, т.е. соответствием пространственной координаты

-τ, т.е. соответствием пространственной координаты ![]() входящего цифрового тракта и временной координаты tg1 в сверхтракте; i = 0,7; S = i+8. Таким образом, для нулевого тракта S0 = 8, для седьмого S7 = 7+8 = 15. Первые восемь разрядов регистра служат для выполнения последовательно-параллельного преобразования, а остальные - для мультиплексирования. Временная коммутация (преобразование

входящего цифрового тракта и временной координаты tg1 в сверхтракте; i = 0,7; S = i+8. Таким образом, для нулевого тракта S0 = 8, для седьмого S7 = 7+8 = 15. Первые восемь разрядов регистра служат для выполнения последовательно-параллельного преобразования, а остальные - для мультиплексирования. Временная коммутация (преобразование ![]() ) выполняется в блоке памяти 256x8 (256 каналов по 8 бит данных). Третий этап процесса коммутации

) выполняется в блоке памяти 256x8 (256 каналов по 8 бит данных). Третий этап процесса коммутации ![]() -τ включает демультиплексирование и последующее преобразование из параллельной формы в последовательную. Он реализуется на демультиплексоре, управляемом счетчиком исходящих трактов С42 и группой регистров RG. Следует отметить, что если в системе АТСЭ-200 МПВК выполнялся на универсальных элементах, то в системе U Т МПВК выполнен в виде заказной специализированной коммутационной БИС.

-τ включает демультиплексирование и последующее преобразование из параллельной формы в последовательную. Он реализуется на демультиплексоре, управляемом счетчиком исходящих трактов С42 и группой регистров RG. Следует отметить, что если в системе АТСЭ-200 МПВК выполнялся на универсальных элементах, то в системе U Т МПВК выполнен в виде заказной специализированной коммутационной БИС.

Из [l] известна аналогичная БИС, содержащая, кроме блока коммутации, узел периферийного управления. Эта специализированная коммутационная БИС реализована по n -МОП- Si технологии, содержит 22x103 транзисторов, оформлена в виде 28-выводного корпуса и обеспечивает коммутацию восьми двухнаправленных полюсов.

На базе МПВК 8x8 в системе UT строятся коммутационные матрицы 16x16, используемые также в коммутационном поле. На рис. 16 приведена их структура.

5.5. Коммутационный модуль системы 12

|

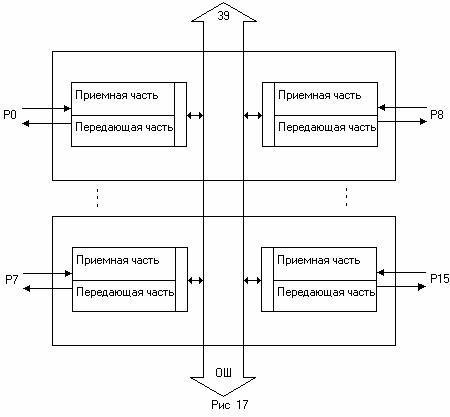

В общем случае модуль реализует пространственно-временную коммутацию 512 цифровых каналов максимум 16 цифровых трактов, каждый на 32 канала. Уровень технологии на период разработки определил подход к построению МПВК из стандартных блоков, представляющих собой каждый сдвоенный коммутационный порт, причем один порт служит для подключения одного ИКМ-тракта. Таким образом, блок имеет параметры 2x2. На рис. 17 показана структура блока и модуля. Как видим, модуль МПВК системы 12 состоит из 16 идентичных двусторонних коммутационных портов Рi , i = 0,15, и общей магистрали - системы шин, c которой соединены все порты и через которые осуществляется их взаимодействие. Каждая пара портов Рi и Рi+7 образует один блок, а 8 блоков, подключенных к общей магистрали, образуют 16-портовый МПВК. Особенностью МПВК системы 12 является то, что на порт заводатся цифровой тракт ИКМ на 32 канала, но длина канального слова равна двум байтам, т.е. вдвое больше длины канального слова системи передачи ИКМ 30/32. Поэтому скорость цифрового потока в модуле овстеш 12 составляет 4096 кбит/с, а не 2048 кбит/с, как в системе ИКМ 30/32.

Технологически каждый блок оформлен в виде БИС, которая является не универсальной, а заказной - специалвзировавной коммутационной БИС. Полный модуль системы 12 на 16 портов занимает одну плату, на. которой размещаются 8 блоков (БИС).

Особенностью МПВК системы 12 является возможность реализации на его основе коммутационных матриц, с различныма параметрами n входов и m выходов, но с соблюдением условия: n≤16 , m≤16, n +m≤16.

Теперь остановимся на характере процесса коммутации в МПВК и особенностях его реализации.Как мы отмечали ,МПВК реализует пространственно-временную коммутацию каналов, но проесс коммутации имеет вид ![]()

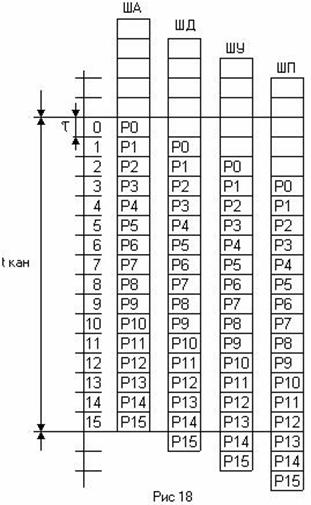

![]() φτ . Следовательно, имеет место преобразование пространственной координаты во временную. Рассмотрим этот вопрос подробнее. Поскольку каждый цифровой тракт подключен к определенному порту, то этап пространственной коммутации сводится к коммутации портов. Поскольку все порты связаны между собой общей магистралью, то, очевидно, именно с ее помощью и реализуется этот этап. Общая магистраль представляет собой систему шин шести типов, общей проводностью 39: шина данных - проводность 16, шина адреса канала - 5, шина адреса порта - 4, шина подтверждения - 5, шина управления - 6, шина синхронизации - 3. Общая магистраль работает в режиме разделения времени так, что в течение каждого временного интервала ti одного канала каждый порт получает доступ к любому другому порту в течение битового интервала τi . Если требуется скоммутировать порт 0 с портом 15, то приемная часть порта 0, где происходит накопление информации заведенного на этот порт цифрового тракта, получит доступ к ОШ в момент τ15 , что будет указано на шине адреса порта. Таким образом, осуществляется пространственная коммутация. Временное разделение ОШ сопровождается достаточно высокими требованиями к элементной базе в части быстродействия. Рассчитаем временной цикл общей шины TОШ. Каждый порт использует общую шину 32 раза за цикл (ИКМ), следовательно,

φτ . Следовательно, имеет место преобразование пространственной координаты во временную. Рассмотрим этот вопрос подробнее. Поскольку каждый цифровой тракт подключен к определенному порту, то этап пространственной коммутации сводится к коммутации портов. Поскольку все порты связаны между собой общей магистралью, то, очевидно, именно с ее помощью и реализуется этот этап. Общая магистраль представляет собой систему шин шести типов, общей проводностью 39: шина данных - проводность 16, шина адреса канала - 5, шина адреса порта - 4, шина подтверждения - 5, шина управления - 6, шина синхронизации - 3. Общая магистраль работает в режиме разделения времени так, что в течение каждого временного интервала ti одного канала каждый порт получает доступ к любому другому порту в течение битового интервала τi . Если требуется скоммутировать порт 0 с портом 15, то приемная часть порта 0, где происходит накопление информации заведенного на этот порт цифрового тракта, получит доступ к ОШ в момент τ15 , что будет указано на шине адреса порта. Таким образом, осуществляется пространственная коммутация. Временное разделение ОШ сопровождается достаточно высокими требованиями к элементной базе в части быстродействия. Рассчитаем временной цикл общей шины TОШ. Каждый порт использует общую шину 32 раза за цикл (ИКМ), следовательно,

ТОШ =![]() =244 нс.

=244 нс.

Доступ к шине для портов организован на основе сверхцикла (рис. 18).

Как мы отмечали, ОШ - это система шести типов шин. Разделение каждой из шин - управления, обмена, подтверждения и др. - производится также во времени аналогично рассмотренному, но со сдвигом для каждой - на один битовый интервал τ.

Временная коммутация каналов осуществляется в блоке временной коммутации (БВК), реализованном на ОЗУ. БВК размещается в передающей части каждого порта и работает в режиме (→↕;↓→) .

|

Таким образом, после завершения пространственной коммутации накопленная в приемной части порта-источника Р0 информация канала ki- передается в ОЗУ порта-назначения Р15 и записывается в соответствии с режимом работы ОЗУ в ячейку с адресом канала назначения kj , который указывается на шине адреса канала. Считывание информации в выбранной временной канал порта P15 производитcя циклически. На этом данный этап установления соединения завершается.

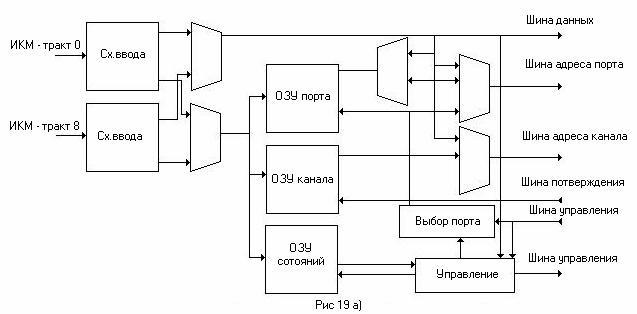

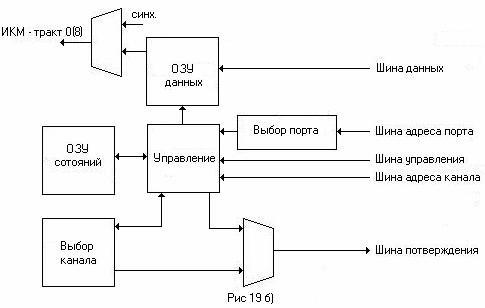

Функциональная схема 16 портового модуля МПВК системы 12 показана на рис. 19,а и 19,б, соответственно приемная и передающая части.

Список литературы

1. Ершова Э.Б. , Ершов Б. А. Цифровые системы распределения информации. - М. : Радио и связь, 1983.

2. Ершова Э.Б. Цифровые системы коммутации с распределенным микропроцессорным управлением на микропроцессорных наборах. - М. : 1986

3. Боккер П. ISDN. Цифровая связь с интеграцией служб. Понятия, методы, системы / Пер. с нем. Под ред. Э.Б.Ершовой. - М.: Радио и связь, 1991.

4. Беллами Дж. Цифровая телефония / Пер. с англ. Э.Б.Ершовой и Э.В. Кординского. - М.: Радио и связь, 1986.

5. Применение интегральных микросхем в электронной вычислительной технике. - М.: Радио и связь, 1987.

6. Фирменные материалы ITALTEL по системе " UT- Linea ".

7. Special issue on System 12. Electrical communication. V. 56, N 2, 3, 1981.

8. Speciale Doppelausgabe die Systeme 12. Elektrisches Nachrichtenwesen. B. 59, N 1,2, 1985.

9. Фирменные материалы А/О ТЕАЕНОКИА по системе DX-200