5.1. Структурирование процесса цифровой коммутации каналов

5.2. Методы структурного синтеза МПВК

5.3. Коммутационный модуль системы ЭАТС-200

5.1. Структурирование процесса цифровой коммутации каналов

Рассмотренные ранее процессы коммутации предполагали для своей реализации разделение блока пространственной и временной коммутации цифровых каналов. Однако теоретически была доказана эффективность комбинированной коммутации и создания универсальных модулей пространственно-временной коммутации МПВК. Реализация этого стала возможной лишь с созданием более современной технологии, которая позволяет строить не только универсальные, но и специализированные БИС, в том числе и с настраиваемой структурой. В настоящее время существуют различные способы структурирования процесса пространственно-временной коммутации, каждый из которых определяет метод синтеза модуля МПКВ.

Рассмотрим процесс коммутации на примере. Пусть требуется скоммутировать два канала ki и kj :

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj }

, tj }

где i = ![]() ; j =

; j = ![]() ; S1,SM ª S; ti , tj ª T

; S1,SM ª S; ti , tj ª T

Распишем., процесс с коммутации для каждого варианта суруктуры.

1. Æ =φSφτ ;

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj },

, tj },

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj };

, tj };

2. Æ =φτ φS,

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj },

, tj },

kj{ ![]() , tj } ® kj{

, tj } ® kj{ ![]() , tj };

, tj };

3. Комбинированная коммутация осуществляется путем двойного эквивалентного преобразования (фиксированного): пространственной координаты

Si ª S в дополнительную временную tgiª Tg - преобразование ![]() и обратное преобразование

и обратное преобразование ![]() . При этом выполняется однозначное соответствие:

. При этом выполняется однозначное соответствие:

Si↔tgi , S↔Tg .

Тогда процесс коммутации протекает так:

Æ =![]() φτ

φτ ![]() ;

;

ki{ ![]() , ti } ® kn{

, ti } ® kn{ ![]() , ti};

, ti};

kn{ ![]() , ti } ® km{

, ti } ® km{ ![]() , tj };

, tj };

ki{ ![]() , ti } ® kj{

, ti } ® kj{ ![]() , tj }.

, tj }.

Легко видеть, что фиксированное преобразование ![]() описывает процесс мультиплексирования (каналообразования в соединительном сверхтракте), а преобразование

описывает процесс мультиплексирования (каналообразования в соединительном сверхтракте), а преобразование ![]() - процесс демультиплексирования.

- процесс демультиплексирования.

5.2. Методы структурного синтеза МПВК

Методы структурного синтеза модуля пространственно-временной коммутации цифровых каналов определяются во многом возможностями технологии. При построении МПВК на базе универсальных ИС средней и большой степени интеграции все преобразования (во времени, в пространстве, параллельно-последовательное и обратное, мультиплексирование и демультиплексирование) выполняются в отдельных функциональных узлах, объединяемых в схему в соответствии с реализуемым процессом.

|

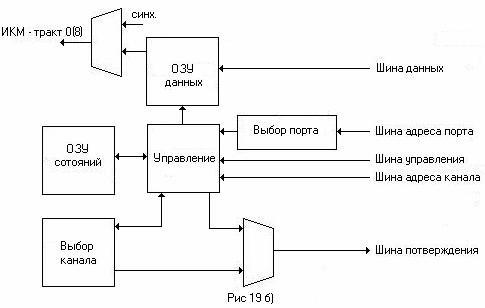

На pиc. 12 приведены три базовые структуры МПВК, которые положены в основу коммутационных модулей цифровых систем коммутации. Первая структура реализует последовательность (S-T), вторая (T-S), третья {(Т/ S) Т(Т/S)}. Каждая из них с той или иной модификацией нашла применение в конкретных системах. Рассмотрим некоторые из них.

5.3. Коммутационный модуль системы ЭАТС-200

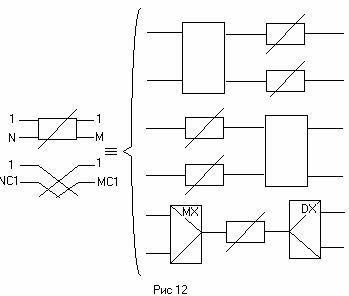

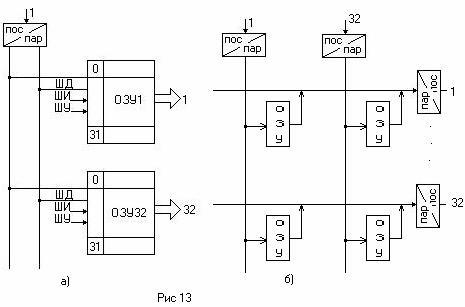

Модуль реализует Æ =φτ φS на множестве цифровых каналов N=1024, образованных в n = 32 цифровых трактов ИКМ по 32 канала в каждом. Учитывая уровень технологии на этапе разработки системы ЭАТС-200, был принят параллельный способ ввода информации в ОЗУ, поэтому на входе и выходе модуля устанавливаются устройства последовательно-параллельного и параллельно-последовательного преобразования соответственно. Их введение, как мы уже отмечали при синтезе МВК, позволяет, с одной стороны, снизить требования к быст-родействию элементной базы, а с другой стороны, обеспечить приемлемую скорость коммутационных процессов при временном преобразовании.

Рассмотрим реализацию коммутационных процессов в модуле: временное преобразование φτ осуществляется в памяти - ОЗУ, пространственное φS - физическим разделением выходов в пространстве. Рис. 13,а иллюстрирует принцип построения компоненты модуля для одного входящего тракта. Как видим, каждый исходящий тракт связан с одним ОЗУ, поэтому для 32 трактов введено 32 ОЗУ. В модуле выбран режим работы ОЗУ - (→↓;↕→). Поэтому технологически процесс cтроится так. В течение каждого цикла передачи Тц информация всех каналов тракта передачи записывается последовательно в одноименные ячейки всех 32 ОЗУ. Таким образом, частота обновления или подтверждения информации в памяти определяется циклом передачи и составляет для данного случая 8 кГц. Поэтому иногда информационный блок цикла называют 8-килогерцевым блоком. Управление коммутацией сводится к выбору соответствующего требованию ОЗУ - пространственная коммутация входящего тракта с исходящим, и выбору ячейки выбранного ОЗУ для считывания информации - временная коммутация цифровых каналов в скоммутированных трактах.

При построении МПВК в системе АТСЭ-200 используется метод двойной памяти, т.е. ОЗУ выполняется на двух идентичных параллельных схемах. Это позволяет использовать элементы памяти, в которых тактовая частота лежит в пределах 8 МГц. Если учесть период разработки системы и имеющиеся пределы допустимого быстродействия элементной базы того времени - тактовая частота до 10 МГц, то такое решение в построении МПВК становится вполне понятным. Модуль набирается из 32 компонент 1x32, как показано на рис. 13,б, путем объединения одноименных выходов. Для того, чтобы скоммутировать канал kiЦТ1 с каналом kjЦT32, необходимо установить полное дуплексное соединение, т.е.

kiЦТ1 → kjЦT32

kjЦT32 → kiЦТ1

Следовательно, пропускная способность коммутационного модуля составляет максимум 16 соединений.

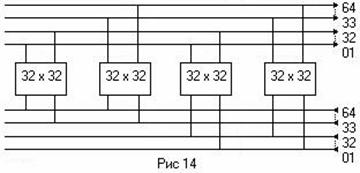

Модуль МПВК 32x32 является базовым модулем системы АТСЭ-200. На его основе строятся ступени искания системы емкостью 96x96; 128x128; 256x256 цифровых трактов. Построение осуществляется стандартным запараллеливанием входов и выходов МПВК, число которых выбирается в зависимости от требуемой емкости. Структуры получаются неэкономичными в силу квадратичной зависимости объёма оборудования от емкости системы. Например, если требуется построить коммутационный блок 64x64, т.е. увеличить емкость модуля вдвое, то для этого потребуется четыре модуля 32x32, т.е. четырехкратное увеличение оборудования (рис. 14).

|

5.4. Коммутационный модуль системы "Линия U Т"

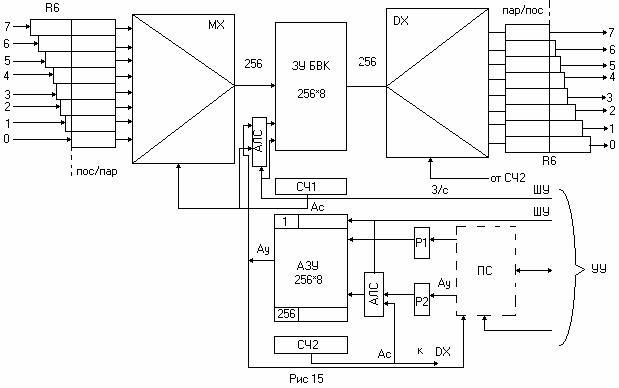

Модуль реализует процесс коммутации Æ =![]() φτ

φτ ![]() для 256 цифровых каналов восьми цифровых трактов ИКМ, каждый на 32 канала. Таким образом, параметры МПВК: 8x8 трактов или 256x256 цифровых каналов. Рис. 15 иллюстрирует принцип построения МПВК и реализацию процесса коммутации.

для 256 цифровых каналов восьми цифровых трактов ИКМ, каждый на 32 канала. Таким образом, параметры МПВК: 8x8 трактов или 256x256 цифровых каналов. Рис. 15 иллюстрирует принцип построения МПВК и реализацию процесса коммутации.

Первый этап процесса коммутации ![]() -τ включает преобразование из последовательной формы в параллельную и последующее мультиплексирование. Он реализуется группой сдвигающих и буферных регистров RG, приданных каждому входящему цифровому тракту, и мультиплексором MX, управляемым счетчиком входящих трактов С41 . Число разрядов Si каждого регистра определяется длиной кодового слова (для ИКМ - 8 бит) и преобразованием

-τ включает преобразование из последовательной формы в параллельную и последующее мультиплексирование. Он реализуется группой сдвигающих и буферных регистров RG, приданных каждому входящему цифровому тракту, и мультиплексором MX, управляемым счетчиком входящих трактов С41 . Число разрядов Si каждого регистра определяется длиной кодового слова (для ИКМ - 8 бит) и преобразованием ![]() -τ, т.е. соответствием пространственной координаты

-τ, т.е. соответствием пространственной координаты ![]() входящего цифрового тракта и временной координаты tg1 в сверхтракте; i = 0,7; S = i+8. Таким образом, для нулевого тракта S0 = 8, для седьмого S7 = 7+8 = 15. Первые восемь разрядов регистра служат для выполнения последовательно-параллельного преобразования, а остальные - для мультиплексирования. Временная коммутация (преобразование

входящего цифрового тракта и временной координаты tg1 в сверхтракте; i = 0,7; S = i+8. Таким образом, для нулевого тракта S0 = 8, для седьмого S7 = 7+8 = 15. Первые восемь разрядов регистра служат для выполнения последовательно-параллельного преобразования, а остальные - для мультиплексирования. Временная коммутация (преобразование ![]() ) выполняется в блоке памяти 256x8 (256 каналов по 8 бит данных). Третий этап процесса коммутации

) выполняется в блоке памяти 256x8 (256 каналов по 8 бит данных). Третий этап процесса коммутации ![]() -τ включает демультиплексирование и последующее преобразование из параллельной формы в последовательную. Он реализуется на демультиплексоре, управляемом счетчиком исходящих трактов С42 и группой регистров RG. Следует отметить, что если в системе АТСЭ-200 МПВК выполнялся на универсальных элементах, то в системе U Т МПВК выполнен в виде заказной специализированной коммутационной БИС.

-τ включает демультиплексирование и последующее преобразование из параллельной формы в последовательную. Он реализуется на демультиплексоре, управляемом счетчиком исходящих трактов С42 и группой регистров RG. Следует отметить, что если в системе АТСЭ-200 МПВК выполнялся на универсальных элементах, то в системе U Т МПВК выполнен в виде заказной специализированной коммутационной БИС.

Из [l] известна аналогичная БИС, содержащая, кроме блока коммутации, узел периферийного управления. Эта специализированная коммутационная БИС реализована по n -МОП- Si технологии, содержит 22x103 транзисторов, оформлена в виде 28-выводного корпуса и обеспечивает коммутацию восьми двухнаправленных полюсов.

На базе МПВК 8x8 в системе UT строятся коммутационные матрицы 16x16, используемые также в коммутационном поле. На рис. 16 приведена их структура.

5.5. Коммутационный модуль системы 12

|

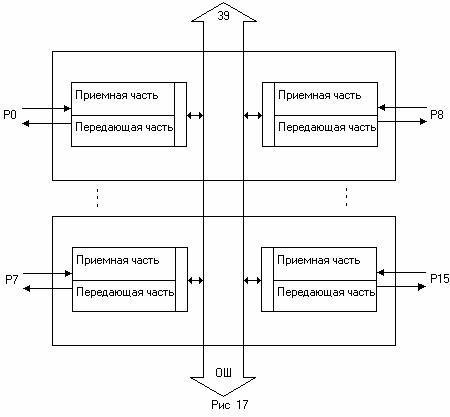

В общем случае модуль реализует пространственно-временную коммутацию 512 цифровых каналов максимум 16 цифровых трактов, каждый на 32 канала. Уровень технологии на период разработки определил подход к построению МПВК из стандартных блоков, представляющих собой каждый сдвоенный коммутационный порт, причем один порт служит для подключения одного ИКМ-тракта. Таким образом, блок имеет параметры 2x2. На рис. 17 показана структура блока и модуля. Как видим, модуль МПВК системы 12 состоит из 16 идентичных двусторонних коммутационных портов Рi , i = 0,15, и общей магистрали - системы шин, c которой соединены все порты и через которые осуществляется их взаимодействие. Каждая пара портов Рi и Рi+7 образует один блок, а 8 блоков, подключенных к общей магистрали, образуют 16-портовый МПВК. Особенностью МПВК системы 12 является то, что на порт заводатся цифровой тракт ИКМ на 32 канала, но длина канального слова равна двум байтам, т.е. вдвое больше длины канального слова системи передачи ИКМ 30/32. Поэтому скорость цифрового потока в модуле овстеш 12 составляет 4096 кбит/с, а не 2048 кбит/с, как в системе ИКМ 30/32.

Технологически каждый блок оформлен в виде БИС, которая является не универсальной, а заказной - специалвзировавной коммутационной БИС. Полный модуль системы 12 на 16 портов занимает одну плату, на. которой размещаются 8 блоков (БИС).

Особенностью МПВК системы 12 является возможность реализации на его основе коммутационных матриц, с различныма параметрами n входов и m выходов, но с соблюдением условия: n≤16 , m≤16, n +m≤16.

Теперь остановимся на характере процесса коммутации в МПВК и особенностях его реализации.Как мы отмечали ,МПВК реализует пространственно-временную коммутацию каналов, но проесс коммутации имеет вид ![]()

![]() φτ . Следовательно, имеет место преобразование пространственной координаты во временную. Рассмотрим этот вопрос подробнее. Поскольку каждый цифровой тракт подключен к определенному порту, то этап пространственной коммутации сводится к коммутации портов. Поскольку все порты связаны между собой общей магистралью, то, очевидно, именно с ее помощью и реализуется этот этап. Общая магистраль представляет собой систему шин шести типов, общей проводностью 39: шина данных - проводность 16, шина адреса канала - 5, шина адреса порта - 4, шина подтверждения - 5, шина управления - 6, шина синхронизации - 3. Общая магистраль работает в режиме разделения времени так, что в течение каждого временного интервала ti одного канала каждый порт получает доступ к любому другому порту в течение битового интервала τi . Если требуется скоммутировать порт 0 с портом 15, то приемная часть порта 0, где происходит накопление информации заведенного на этот порт цифрового тракта, получит доступ к ОШ в момент τ15 , что будет указано на шине адреса порта. Таким образом, осуществляется пространственная коммутация. Временное разделение ОШ сопровождается достаточно высокими требованиями к элементной базе в части быстродействия. Рассчитаем временной цикл общей шины TОШ. Каждый порт использует общую шину 32 раза за цикл (ИКМ), следовательно,

φτ . Следовательно, имеет место преобразование пространственной координаты во временную. Рассмотрим этот вопрос подробнее. Поскольку каждый цифровой тракт подключен к определенному порту, то этап пространственной коммутации сводится к коммутации портов. Поскольку все порты связаны между собой общей магистралью, то, очевидно, именно с ее помощью и реализуется этот этап. Общая магистраль представляет собой систему шин шести типов, общей проводностью 39: шина данных - проводность 16, шина адреса канала - 5, шина адреса порта - 4, шина подтверждения - 5, шина управления - 6, шина синхронизации - 3. Общая магистраль работает в режиме разделения времени так, что в течение каждого временного интервала ti одного канала каждый порт получает доступ к любому другому порту в течение битового интервала τi . Если требуется скоммутировать порт 0 с портом 15, то приемная часть порта 0, где происходит накопление информации заведенного на этот порт цифрового тракта, получит доступ к ОШ в момент τ15 , что будет указано на шине адреса порта. Таким образом, осуществляется пространственная коммутация. Временное разделение ОШ сопровождается достаточно высокими требованиями к элементной базе в части быстродействия. Рассчитаем временной цикл общей шины TОШ. Каждый порт использует общую шину 32 раза за цикл (ИКМ), следовательно,

ТОШ =![]() =244 нс.

=244 нс.

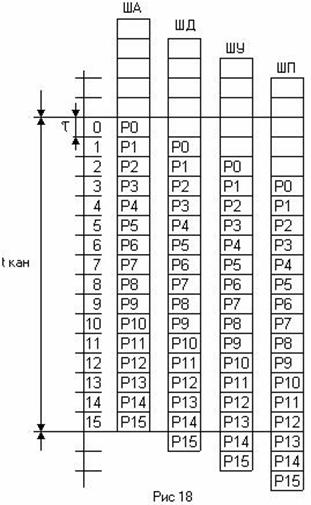

Доступ к шине для портов организован на основе сверхцикла (рис. 18).

Как мы отмечали, ОШ - это система шести типов шин. Разделение каждой из шин - управления, обмена, подтверждения и др. - производится также во времени аналогично рассмотренному, но со сдвигом для каждой - на один битовый интервал τ.

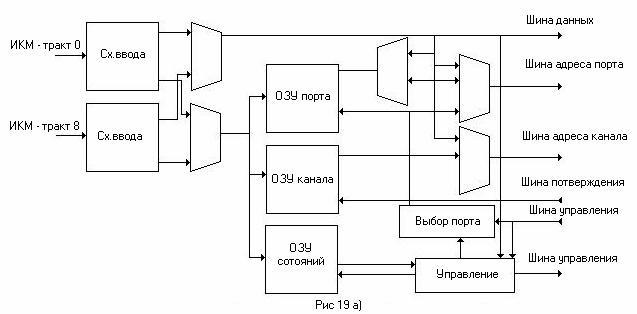

Временная коммутация каналов осуществляется в блоке временной коммутации (БВК), реализованном на ОЗУ. БВК размещается в передающей части каждого порта и работает в режиме (→↕;↓→) .

|

Таким образом, после завершения пространственной коммутации накопленная в приемной части порта-источника Р0 информация канала ki- передается в ОЗУ порта-назначения Р15 и записывается в соответствии с режимом работы ОЗУ в ячейку с адресом канала назначения kj , который указывается на шине адреса канала. Считывание информации в выбранной временной канал порта P15 производитcя циклически. На этом данный этап установления соединения завершается.

Функциональная схема 16 портового модуля МПВК системы 12 показана на рис. 19,а и 19,б, соответственно приемная и передающая части.